@Vengineerの戯言 : Twitter SystemVerilogの世界へようこそ、すべては、SystemC v0.9公開から始まった

はじめに

TwitterのTLに流れてきたので読んでみた。The Next Platform の Jim Kelly さんへのインタビュー記事。Tenstorrent: CEO Ljubisa Bajic さんも一緒にインタビューされているけど、ほとんどが Jim Keller さんへのインタビューだった。

メモ

- 推論用のGrayskull は、GF 12nm、LPDDR4 x 8、PCIe Gen4 x16

- 学習用のWormhole は、Grayskull と同じ GF 12nm。メモリは LPDDR4 x8 から GDDR6 x6 に変更。インターコネクト用に x16 100GbE

- 4コアの out of order な ARC CPU にて linux が動いている => これが SiFiveのX280 RISC-V cores, with 512-bit vector extensionsに変わる?

- シリコンサイズ:620 mm2 (for Grayskull)、670 mm2 (for Wormhole).

- Compute core 数:120コア (for Grayskull)、81コア (for Wormhole) <= この図から計算。

- Compute core 間の接続は、2-D

- チップのコストよりケーブルのコストの方が高くなる

- Grayskull と Wormhole 開発に、4000万ドルかけた

- Grayskull 開発は、15名

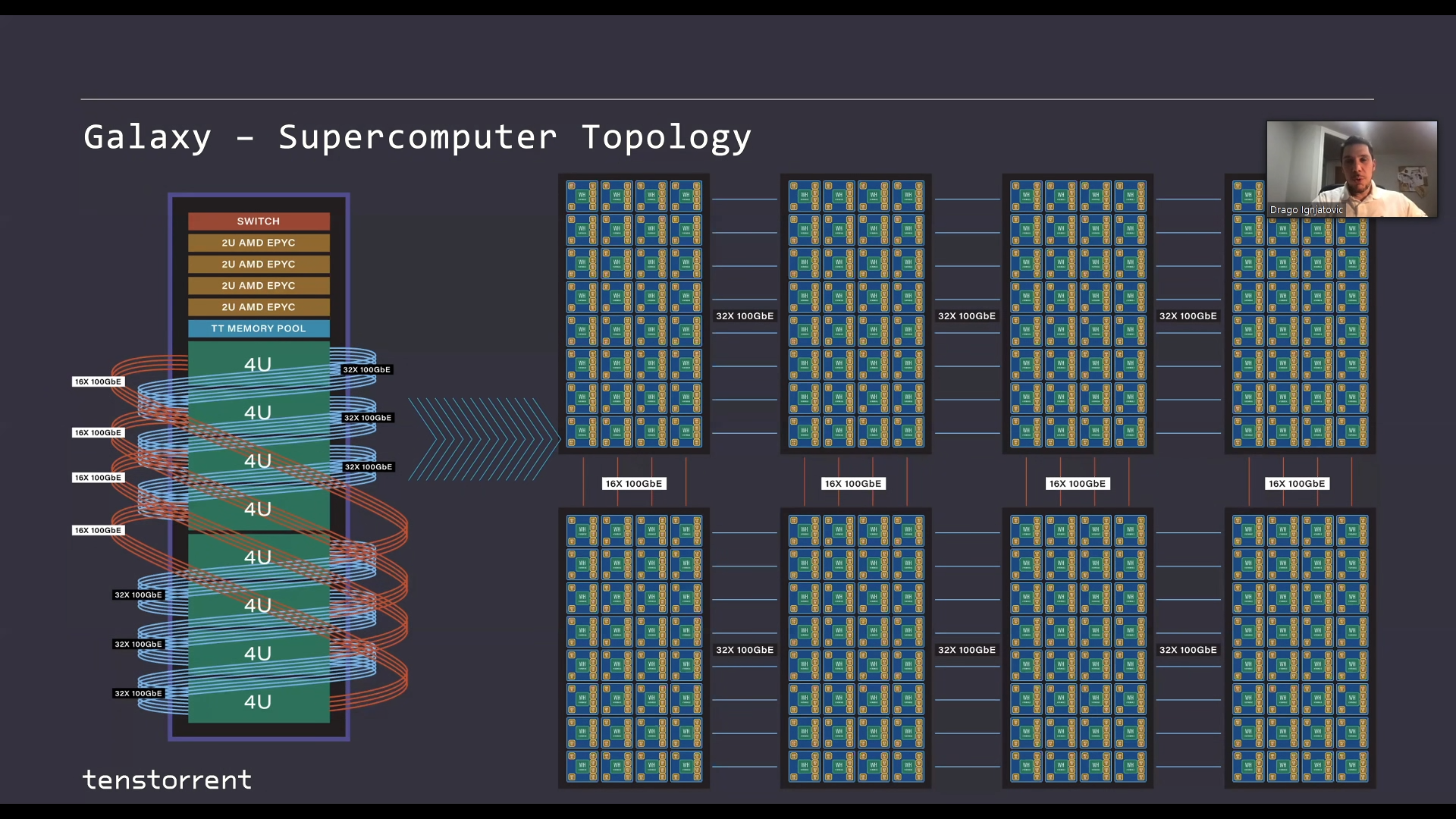

- Wormholeを使ったRack (Galaxy) はこんな感じ(説明のために下図を引用します) => 4U x 8 台で、16 x 16 の構成 (256チップ)の 2-D 構成を実現。Rackには4台の2UのAMD EPYCサーバー搭載 各チップのPCIe Gen4 x16 と 4台のAMD EPYCサーバーをどのように接続しているのかが気になります。1台の4Uに32個のチップが載っているので、1台の2UのAMD EPYCサーバーには64個のチップが接続することになります。AMD EPYC、1チップからx16が4組出てくると考えると1組に8チップが接続される?すごいなー。。。

おわりに

LINLEY SPRING PROCESSSOR CONFERENCE 2021のビデオはユーザー登録しないと見られないので、Tenstorrentの講演ビデオおよびスライドはまだ見ていません。 なので、今回のインタービューにてかなりのことを知ることができたのはよかったです。

追記)、2021.05.31 2021年春の半導体会議で判明した新情報 AIプロセッサーの昨今