はじめに

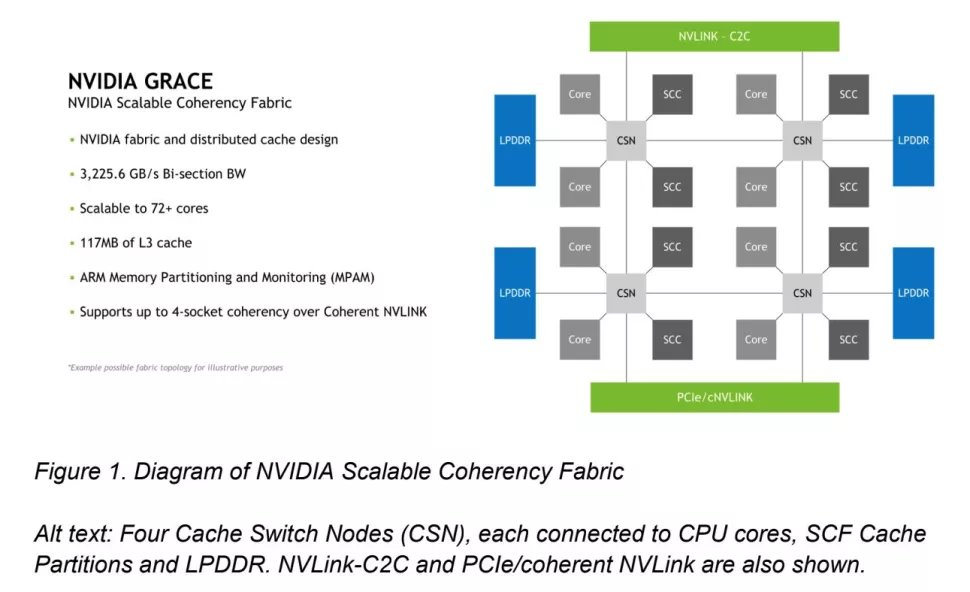

NVIDA GRACEの内部構成がちょっと公開されたのがこれ(説明のために引用します)

これによると、CSN (Cache Switch Nodes) に、SCF Cache と Core が接続されていて、4方向の接続があるというもの

LPDDR5 x16 だと、32コアしか繋げられないので、残りの40コアは、10列x2 (10x2x2)で並んでいるのか?と妄想します。

追記)、2022.11.14 : ここ によると、LPDDR5X の チャネル数は32ということでした。

と書いた後に、いろいろと調べていたら、自分のブログに行きつきました。

下記の写真から上段に(6 x 3) + (6 x 3)、下段に(6 x 4) + (6 x 4) のブロックが2次元に並んでいます。12 x 7 = 84。この内、8個はCPUコアではありません。76個のCPUコアになります。NVIDIAは72コアと言っているので、4コアはスペアですかね。

8個がメモリコントローラ部分になっています。NVIDIAが公開した図だとメモリコントローラは16個あるので、このブロックの中に2個のメモリコントローラに入っています。

L3 Cache が 117MB ということで、72コアだと、1024KB+512MBx72コア = 110,592MB で 6.4MB 違う。1024KB+512KBx76コアとすると、116,736MB となり、117MBというロジックですかね。

下記のツイートの画像が鮮明でした。

Hmmm… how many cores does this mean? pic.twitter.com/W5D3PmOd48

— Longhorn (@never_released) 2021年11月13日

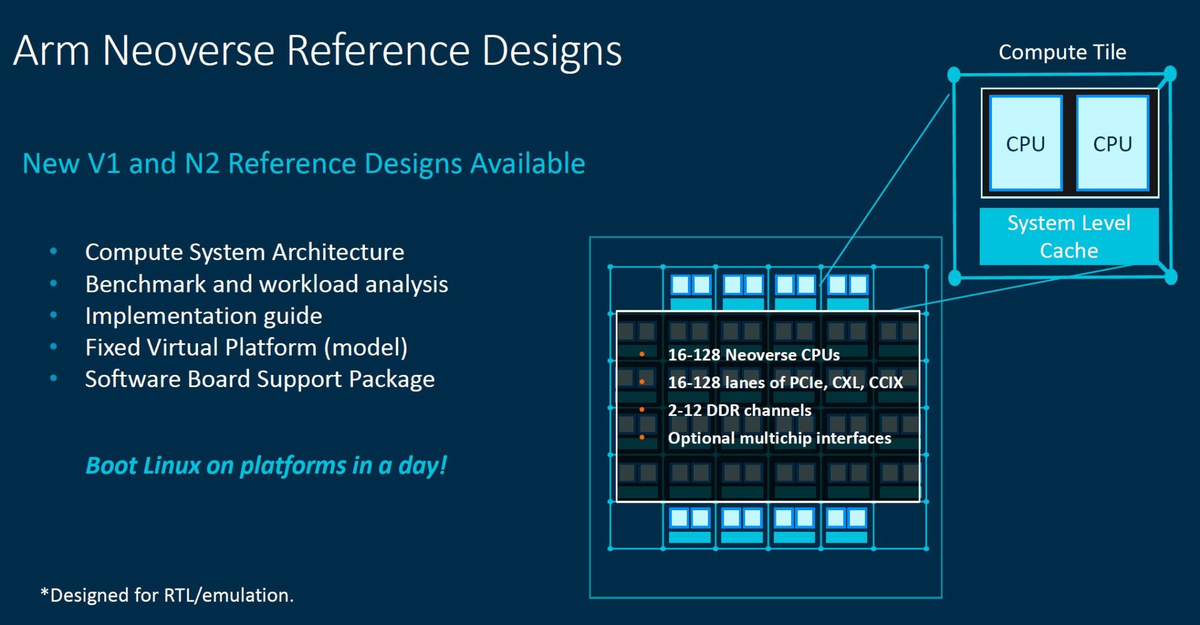

Arm V1/N2 Reference Designs

の中にあった図を説明のために引用します。各Compute Tileには、CPUコア x 2 + System Level Cache であり、これが2次元に並んでいる。

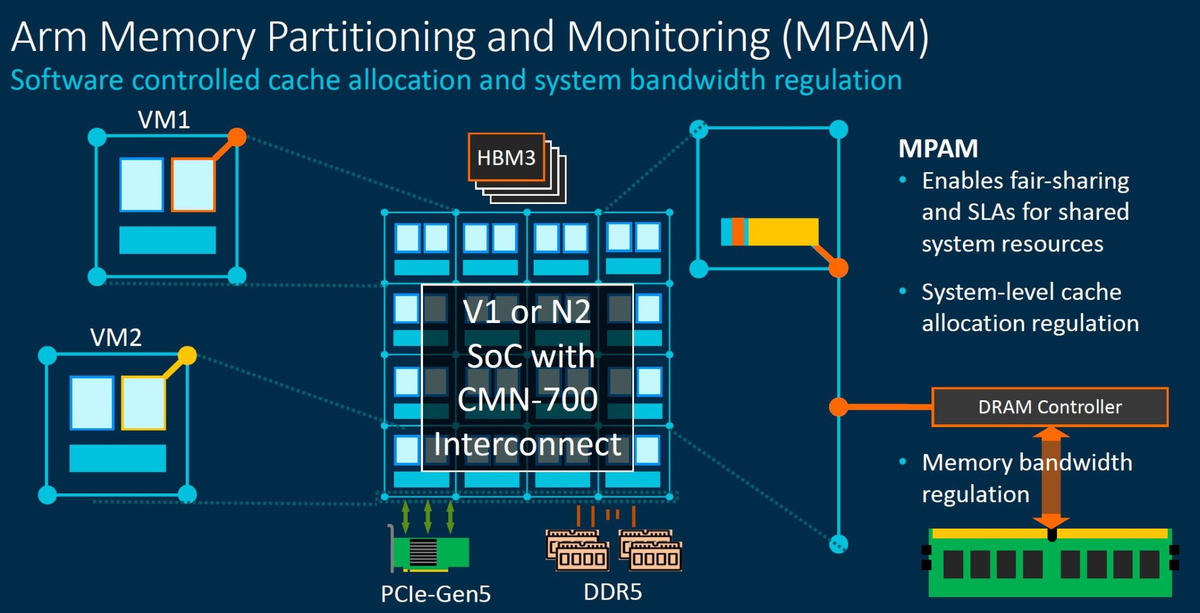

下記も説明のために引用します。右上の System Level Cache と DRAM Controller が接続している感じ。

Memory System Resource Partitioning and Monitoring (MPAM), for A-profile architecture

Memory System Resource Partitioning and Monitoring (MPAM), for A-profile architecture

CMN-700 について、下記のブログに書きました。

Memory System Resource Partitioning and Monitoring (MPAM) について、ちょこっと書いていますね。

おわりに

Arm CMN-700 が2021年4月頃の Arm Tech Day 2021 の発表なので、NVIDIA GRACE では使えないのかなと。そうなると、Arm CMN-600 になります。下図のように(説明のために下図を引用します)、内部接続は 8x8 となり、上記の妄想図では、8 + 10 + 10 + 8 はサポートしていないので、

- NVIDIA fabric and distributed cahe design

というのは、そういうことなのかな?と思っています。