はじめに

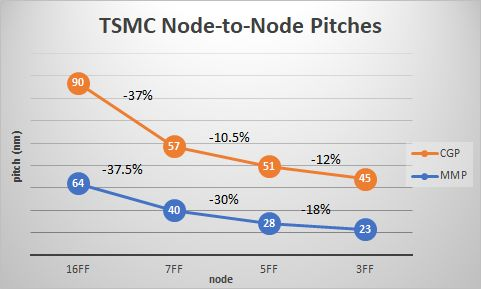

下記のツイートの図。TSMCの Node-To-Node Pitch をグラフにしたものです。

TSMC's 3nm showed no scaling of SRAM (per IEDM 2022), much reduced scaling of metal pitch, and maintained slow scaling of gate pitch, all indications of limited improvements from the most advanced technologies. https://t.co/Bh4beQgEw2

— Fred Chen (@DrFrederickChen) 2023年2月10日

ツイートが無くなる可能性はゼロじゃないので、説明のために図を引用します。

どのぐらい変わったか?

CGP (コンタクトゲートピッチ)は、

- 16nm => 7nm では、90nm => 57nm で、-37%

- 7nm => 3nm では、57nm => 45nm で、-21%

MMP (minimum metal pitch) は、

- 16nm => 7nm では、64nm => 40nm で、-37.5%

- 7nm => 3nm では、40nm => 23nm で、-42.5%

SRAM は?

上記のTweetにもありますが、SRAMに関して明記されていません。

記録のために、Tweetの内容を引用します。

TSMC's 3nm showed no scaling of SRAM (per IEDM 2022), much reduced scaling of metal pitch, and maintained slow scaling of gate pitch, all indications of limited improvements from the most advanced technologies.

5nm => 3nm では、SRAMはほぼサイズは変わりません。

つまり、Logic はたくさん入るが、SRAMは同じだけしか入らない、ということになります。

となると、SRAMたくさんのチップは 5nm => 3nm になっても面積は小さくならないのです。。。

おわりに

TSMC 3nm の SRAM の件は、業界に大きなショックを与えたと思います。じゃー、2nm/1.xnm になってもそうなのか?

そこに登場するのが、CFET(コンプリメンタリFET) です。これで、SRAMが小さくできればいいのですが。。。