はじめ

Intel FPGA Stratix 10 や Agilex 7には、EMIB にて色々な chiplet を接続しています。FPGA と chiplet 間は、Intel AIB (今は、Chips Alliance) を使っているようです。

Intel AIB

AIB は、Advanced Interface Bus の略のようです。Intelから下記のようなドキュメントが公開されています。説明のために色々と引用します。

AIB は Bus です。かつ、SEDESではないです。上記のドキュメントからタイミングチャートです。

SDRとDDRがあります。クロックは 差動ではありません。

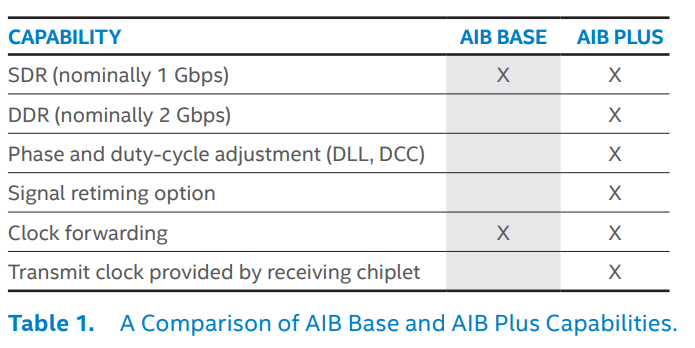

AIB BASE はSDRのみ、AIB PLUS では SDR/DDR です。

Column/Channel 構成です。Column は最大24、Channelは160本までサポート。2Gbps だと、Channelは160本、40GB/s 出ます。双方向で320本必要です。

2つの Die は下記のような感じの配線になっているようです。これを見ると、どの配線も同じになりますね。

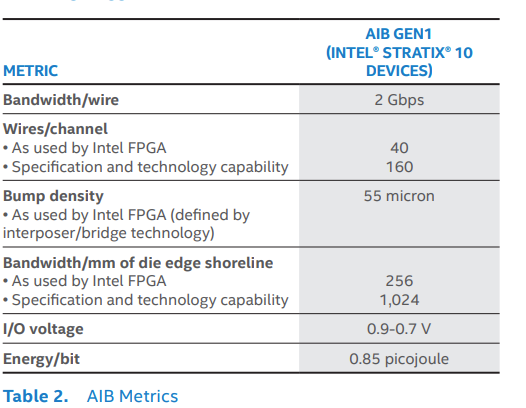

Intel FPGA Stratix 10 では、AIB Gen1 で下記のようになっています。DDR 2Gbps で 40 wires/Channel になっています。40 x 2Gbps = 10GB/s です。

Chips Alliance AIB 2.0

AIB の現在のバージョンは、2.0 です、Chip Alliance の github の AIB-specification に仕様書があります。

下図は、2.0 の仕様書から説明のために引用します。

Gen1 では、SDRで1Gbps、DDRで2Gbpsですが、Gen2 では、DDRのみで 4Gbps/6.4Gbps です。6.4Gbps を使うと、40本で32GB/s、80本で64GB/s になります。

- PCIe Gen4 x16 は片側 32GB/s なので、AIB 2.0 DDR 6.4Gbps を 40本

- PCIe Gen5 x16 は片側 64GB/s なので、AIB 2.0 DDR 6.4Gbps を 80本

Intel FPGA Agilex R-Tile

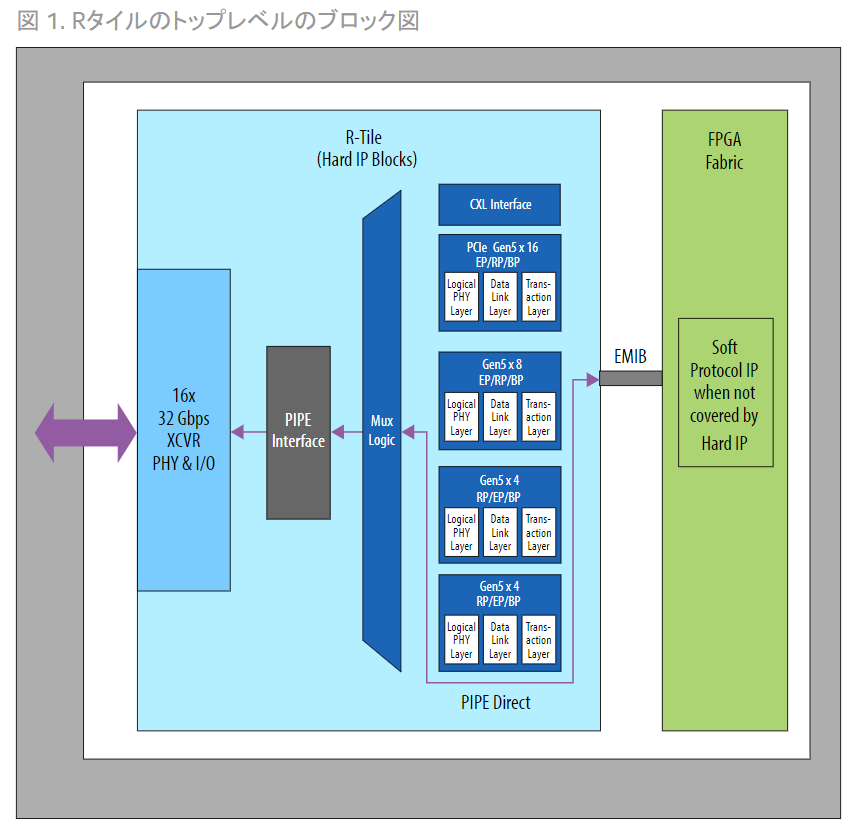

Agilex R-Tileには、下記(説明のために、ここから引用します)のようにPCIe Gen5 IP が入っています。

FPBA Fabric と R-Tile を EMIB にて接続しています。この間のプロトコルは AIB です。PCIe Gen5 x16 だと、片側32GB/s なので AIB Gen2 の DDR/2Gbps だと64 x 8 / 2 = 256本(片側) 必要です。これでは多過ぎるので、AIB Gen2 の DDR/4Gbps を使うと、64 x 8 / 4 = 128本、これでも多そうです。DDR/6.4Gbpsだと 80本になります。

おわりに

SEDESでなくても、6.4Gbps で40本とか80本で転送できるんですね。。。