@Vengineerの戯言 : Twitter

SystemVerilogの世界へようこそ、すべては、SystemC v0.9公開から始まった

今まで、gitee にあった、Huawei の ディープ・ラーニングフレームワークであるMindspore が github に来た?

github.com

サクッて見てみたら、

をサポートしているっぽい。

OSは、Ubuntu と EulerOS (CentOSのHuawei版、Huawei Cloudで使われている)

CPUだけ、Windows 10で動く。EulerOSはAscendのみ。

Mindsporeのバイナリもダウンロードできる模様。

CUDAの時は、NCCL(NVIDIA Collective Communication Library)と使っていて、Ascendの時は、HCCL(Huawei Collective Communication Library)を使って要るっぽい。

HCCLとは、

HCCSはファーウェイが独自に開発した高速相互接続インターフェースで、オンチップRoCEがノード間の直接相互接続に使用できます。

用のライブラリかな。。。

下記の Atlas 900 のページを見ると、

HCCS + PCIe 4.0 + 100 GE

HCCS (Huawei Cache Coherence System)、になっていて、

240 Gbit/s: inter-chip interconnect enabled by HCCS

ともありますね。30GB/s ということは、PCIe Gen4 x16 相当かな、e.huawei.com

昨年(2019年)のHotchip 31 のスライド この分(引用します)にある Hydra SubsysがHCCLのことで、Networkが 100G RoCEなんだろうね。

違う頁には、

- 3x 240Gbps HCCS ports – for NUMA connections

- 2x100Gbps RoCE interfaces for networking

ともあります。ね。

GraphEngineも github にあるんだよね。

github.com

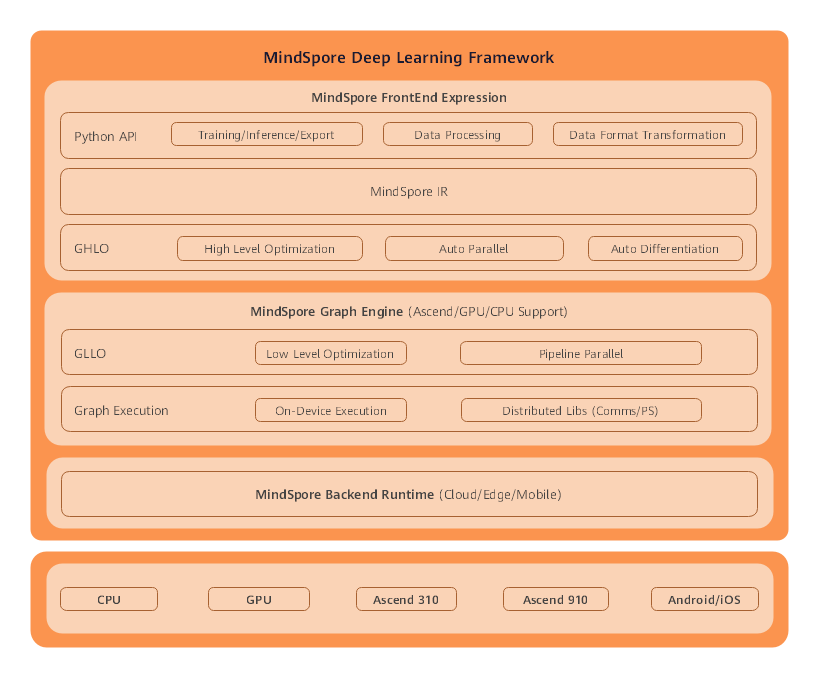

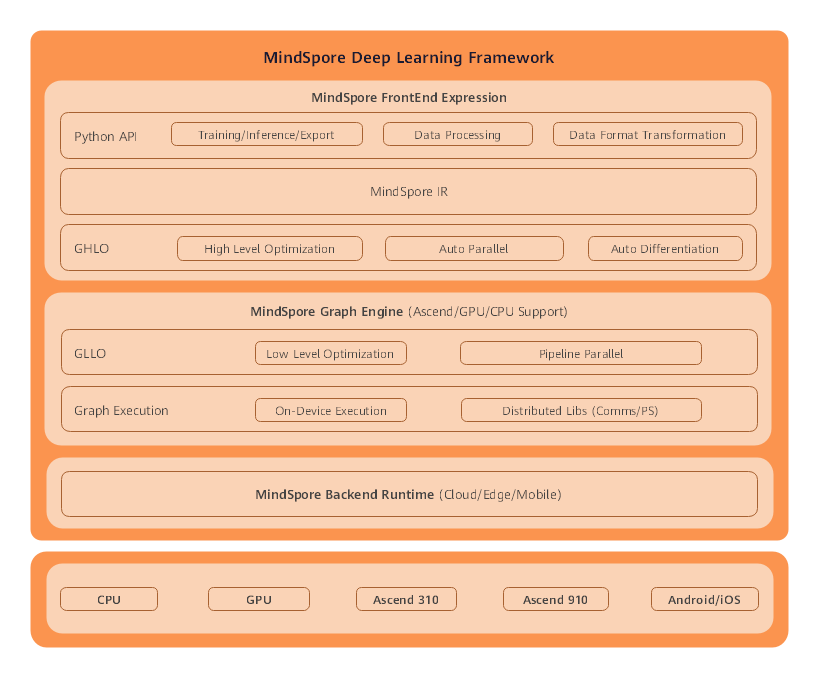

ここにある下記の図(引用します)をみると、ほとんど公開されているのかな?

Backend Runtimeの下のレイヤーは無理でしょうけど。。。

Benchmarkとしては、ここに 0.2.0-alpha の Resnet50 v1.5のデータがあります。

PrecisionはMix(fp16/fp32)、Batch Size=32

- Ascend: 1 * Ascend 910 + CPU:24 Cores => 1787 images/sec

- Ascend: 8 * Ascend 910 + CPU:192 Cores => 13689 images/sec

- Ascend: 16 * Ascend 910 + CPU:384 Cores => 27090 images/sec

大体スケールしている。

Habana Gaudi(現、Intel)のResnet-50のベンチマークが ここ の 22頁目にあって、

- Gaudi x 8 => 13200 images/sec

- Gaudi x 16 => 26400 images/sec

- Gaudi x 32 => 49600 images/sec

となっている。ということは、Gaudiよりちょっと速いということね。