@Vengineerの戯言 : Twitter

SystemVerilogの世界へようこそ、すべては、SystemC v0.9公開から始まった

insidehpc.com

によると、

Neocortex architectureというものは、Cerebras CS-1 AI serversを2台使うと。

The Cerebras servers will be coupled with a HPE Superdome Flex provisioned with 24 terabytes of memory, 205 terabytes of high-performance flash storage, 32 powerful Intel Xeon CPUs, and 24 network interface cards for 1.2 terabits per second of data bandwidth to each Cerebras CS-1, according to PSC.

にあるように、32個のXeonと24本のネットワークカードとCerebras CS-1 と繋げる。

1台の Cerebras CS-1 には、12x standard 100 Gigabit Ethernet が付いているので、2台で24本のネットワークカードになるわけですね。

HPE Superdome Flex って、これかな (PDFファイル) ?

ネットワークは100GbEじゃないので、PCIe にボードさすんですね。

背面を見ると、PCIe は16枚しか刺さらないので、24枚刺すのはどうするのでしょうかね。仕様的には、x16なら56スロット、x8なら72スロットとあるので、

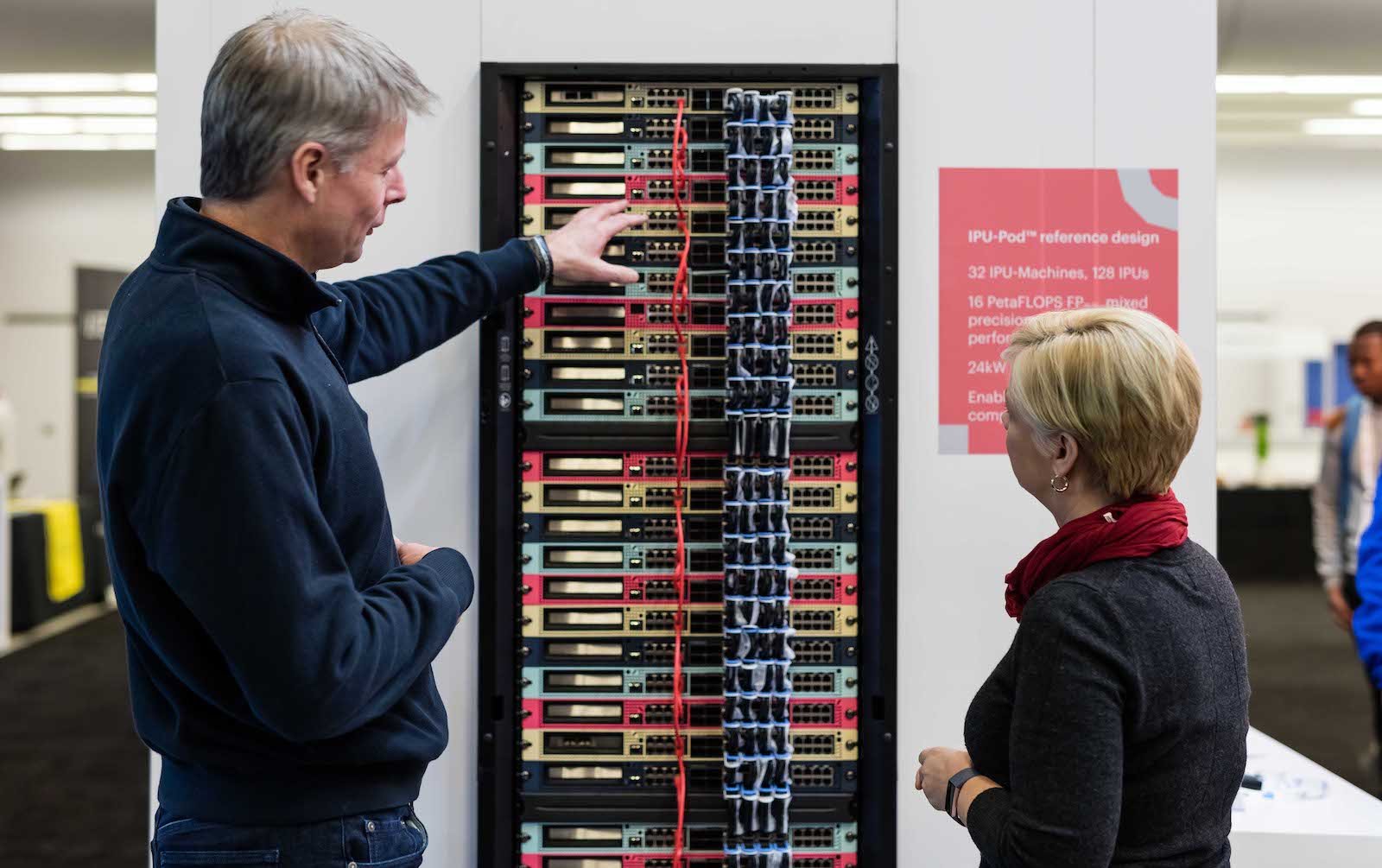

おっと、こちらの資料 (PDFファイル)では、5Uのサーバーには4ソケットしかさせないで、8台使って、32スロットをサポートするようです。

となると、24本のネットワークも8台のどこかに刺せばいいということね。

ここに8台のRackが載っていますね。

32コア間の接続は、HPE Superdome Flex ASICを使って、HPE Superdome Flex Gridを構成するのね。

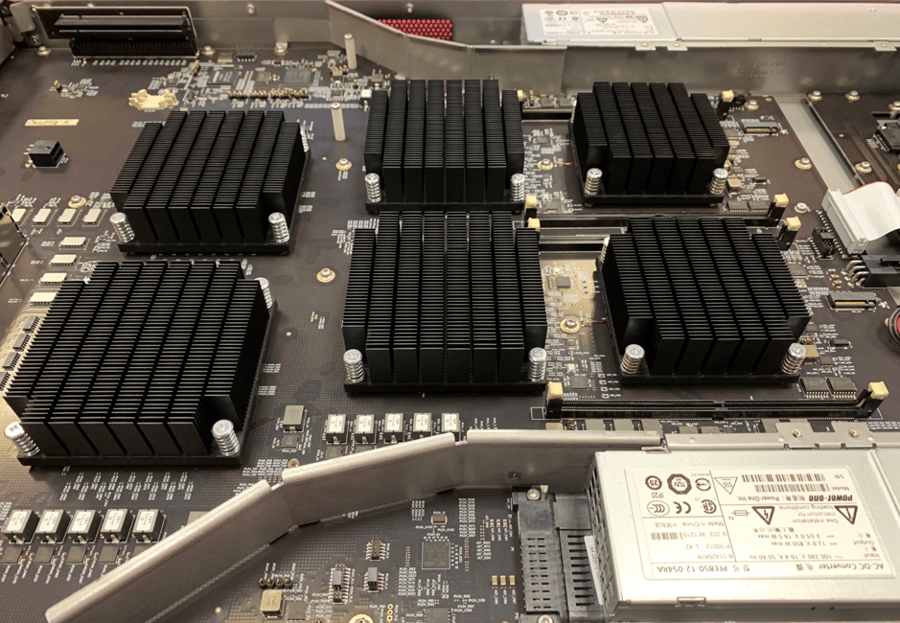

ここにも詳しいブロック図があります。ここには、各ASICから15本でている配線用のコネクタが2組(合計で30個)が前面(カバーを外さないと見られないっぽい)の下側にあります。ここにはもっと詳しいブロック図もあります。

いろいろと調べていったら出てきました

HPE Superdome Flex ASICに採用されているのって、HPが買収したSGIの NUMALink がベースっぽい。

NUMAlink 8 (Flex ASIC)[edit]

NUMAlink 8 is the eighth generation of the interconnect, introduced in 2017 and used in the HPE Superdome Flex. NUMAlink 8 is capable of 853.33 GB/s of bisection peak bandwidth(64 links are cut) for up to 32 socket system and 48TB of coherent shared memory.

とあります。

2017年のNEXTPLATFORMの記事も出てきた。

www.nextplatform.com