はじめに

このブログで取り上げた

- Intel Xeon の Sapphire Rapid

- Intel GPU の Ponte Vecchio

- AMD CPU の EPYC

- AMD GPU の MI200

- Amazon CPU の Graviton3

は、どれも chiplet design です。

かなり前から chiplet design になると言われてきましたが、今年は chiplet design の年になったのでは?

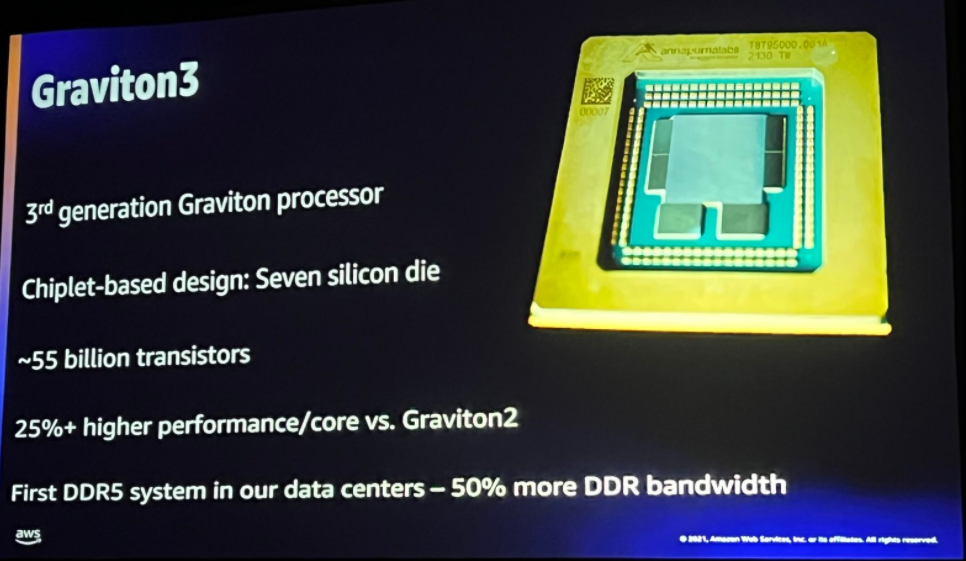

ちょっと違うのが Amazon CPU の Graviton 3

IntelのCPUやGPU、AMDのCPUやGPUは、自社の商品として開発しているものですが、Amazon CPU の Graviton3 はCPUそのものが商品ではありません。クラウドサービスとしてのハードウエアを外部から調達するのではなく、自社で開発しているところがIntelやAMDと違うところです。

2021年12月1日のブログに追記しましたように、Graviton3 は 7 die で構成されています。

Graviton3 が 7 die から構成されているスライドを下記に説明のために引用します。

大きな die の周りの 6 個の die が繋がっています。4つの小さな die は、DDR5用。残りの2 die は、PCIe Gen5用。

どうやら、Silicon Interposer にて各 die を接続していないっぽい。となると、Silicon Bridge なのかな? ブログの追記にも書きましたが、どうやら、Intel Foundry を利用したっぽいです。 下の記事の中に、

ちなみにIntel Foundry Serviceの最初の顧客の1つとして、Amazonがこのパッケージング技術を利用すると明らかにした。おそらくチップそのものはAmazonの子会社であるAnnapurna Labsが開発するArm Neoverseベースの製品で、前工程はインテル以外の可能性があるが、それをインテルの後工程ファブに持ち込んでパッケージングすることを想定していると思われる。

とありますので。各 die は インテルで開発したものではないかもしれませんが、パッケージング技術は Intel、となると die 間は EMIB になりそうですね。

そして、Intel は 下記のようなFPGA Agilex用に PCIe Gen5 用の R-Tile なるものを開発しているので、その R-Tile を EMIB で接続すると自分のところで開発する必要もないし、デバイスドライバもそのまま使えるのでは?

- PCIe Gen5 : R-Tile

- 最大PCIe Gen5 x 16 EPおよびRP

- ポート分岐サポート : 2x8エンドポイントまたは4x4ルートポート

DDR5に対しても、Intel FPGA Agilex でサポートしているので、この部分は Intel にお願いしちゃうというのもありじゃないかな?

なんとなく、DDR5 die と PCIe Gen5 die は見た目似ている(Siliconなのでみんな?同じじゃんが、真ん中の大きいのはちょっと違う)

おわりに

AmazonのCPU Graviton3。みなさん、Graviton/Graviton2 の次なのね。程度だと感じているかもしれませんが、ある意味、大きな進化です。CPU/GPUベンダー以外で chiplet design をやったのですから。

今年も後、1か月もないです。これからどんどん、chiplet design で開発したものが出てくると思います。

大きなところで、NVIDIAの Ampere Next こと、Hopper (H100) です。Silicon Interposer(TSMC CoWoS) にて、2 die + 各die に 4個のHBM2E 。AMD GPU の MI200 と似たような構成です。MI200は Silicon Interposer ではなく、Silicon Bridgeを使っています。

関連記事(追記、2021.01.09)