はじめに

Xilinx Vitis の中を調べるのその14。

今回は、INTERFACE に s_axilite を生成した時に、C/RTL Simulation (Random Stallを ON)での生成されるファイルをみていきます。

axivip

C/RTL Simulation (Random Stall を ON)にした時に生成ファイルは、ちょっとかわりました。

axivip ディレクトリの下に下記のファイルが生成されました。これは、AXI用のUVMベースの検証モデルっぽいです。

ls axivip/ axi_base_sequence.sv axi_master_agent.sv axi_master_wdrv.sv axi_slave_awdrv.sv axi_transfer.sv axi_cfg.sv axi_master_ardrv.sv axi_monitor.sv axi_slave_bdrv.sv axi_type.sv axi_driver_base.sv axi_master_awdrv.sv axi_pkg.sv axi_slave_rdrv.sv axi_virtual_sequencer.sv axi_env.sv axi_master_bdrv.sv axi_sequencer.sv axi_slave_seq_lib.sv axi_if.sv axi_master_rdrv.sv axi_slave_agent.sv axi_slave_wdrv.sv axi_info.sv axi_master_seq_lib.sv axi_slave_ardrv.sv axi_state.sv

sv_module_top.sv

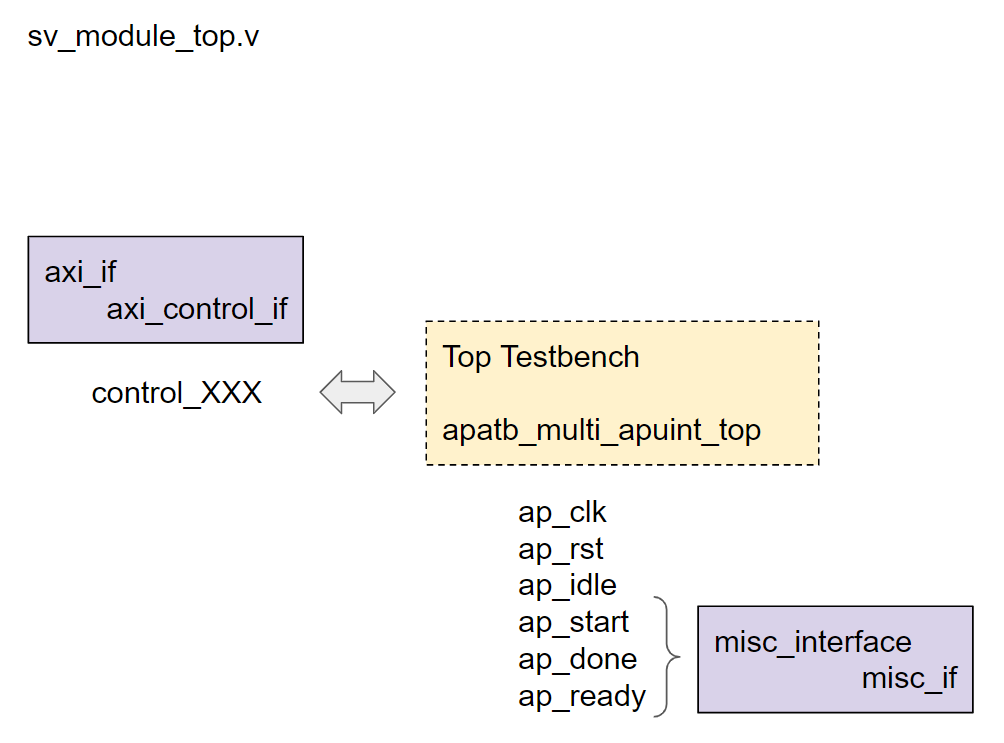

svtb/sv_module_top.sv の中は、下記のようになっています。また、図示してみました。mult_in0/multi_in1/multi_out の svr_if から 1つの axi_if になっています。

//Vitis HLS - High-Level Synthesis from C, C++ and OpenCL v2022.1 (64-bit) //Tool Version Limit: 2022.04 //Copyright 1986-2022 Xilinx, Inc. All Rights Reserved. //============================================================== `ifndef SV_MODULE_TOP_SV `define SV_MODULE_TOP_SV `timescale 1ns/1ps `include "uvm_macros.svh" import uvm_pkg::*; import file_agent_pkg::*; import multi_apuint_subsystem_pkg::*; `include "multi_apuint_subsys_test_sequence_lib.sv" `include "multi_apuint_test_lib.sv" module sv_module_top; misc_interface misc_if ( .clock(apatb_multi_apuint_top.AESL_clock), .reset(apatb_multi_apuint_top.AESL_ reset) ); assign apatb_multi_apuint_top.ap_start = misc_if.tb2dut_ap_start; assign misc_if.dut2tb_ap_done = apatb_multi_apuint_top.ap_done; assign misc_if.dut2tb_ap_ready = apatb_multi_apuint_top.ap_ready; initial begin uvm_config_db #(virtual misc_interface)::set(null, "uvm_test_top.top_env.*", "misc_if", misc_if); end axi_if #(6,4,4,3,1) axi_control_if (.clk (apatb_multi_apuint_top.AESL_clock), .rst(apatb_multi_apuint_top.AESL_res et)); assign apatb_multi_apuint_top.control_AWADDR = axi_control_if.AWADDR; assign apatb_multi_apuint_top.control_AWVALID = axi_control_if.AWVALID; assign axi_control_if.AWREADY = apatb_multi_apuint_top.control_AWREADY; assign apatb_multi_apuint_top.control_WVALID = axi_control_if.WVALID; assign axi_control_if.WREADY = apatb_multi_apuint_top.control_WREADY; assign apatb_multi_apuint_top.control_WDATA = axi_control_if.WDATA; assign apatb_multi_apuint_top.control_WSTRB = axi_control_if.WSTRB; assign apatb_multi_apuint_top.control_ARADDR = axi_control_if.ARADDR; assign apatb_multi_apuint_top.control_ARVALID = axi_control_if.ARVALID; assign axi_control_if.ARREADY = apatb_multi_apuint_top.control_ARREADY; assign axi_control_if.RVALID = apatb_multi_apuint_top.control_RVALID; assign apatb_multi_apuint_top.control_RREADY = axi_control_if.RREADY; assign axi_control_if.RDATA = apatb_multi_apuint_top.control_RDATA; assign axi_control_if.RRESP = apatb_multi_apuint_top.control_RRESP; assign axi_control_if.BVALID = apatb_multi_apuint_top.control_BVALID; assign apatb_multi_apuint_top.control_BREADY = axi_control_if.BREADY; assign axi_control_if.BRESP = apatb_multi_apuint_top.control_BRESP; assign axi_control_if.BID = 0; assign axi_control_if.RID = 0; assign axi_control_if.RLAST = 1; initial begin uvm_config_db #( virtual axi_if#(6,4,4,3,1) )::set(null, "uvm_test_top.top_env.axi_lite_control.*", "vif", axi_c ontrol_if); end initial begin run_test(); end endmodule `endif

下記は、ap_hs の時の sv_module_top.sv を図示したものです。

おわりに

次回は、シナリオファイル (sim/verilog/svtb/multi_apuint_subsys_test_sequence_lib.sv) の中を覗いてみます。