はじめに

調べ物をしていたら見つけたこの論文

色々な情報を得ることができたので、記録として残します。

AMD EPYC ROME の内部構成

AMD EPYC ROME の内部構成のブロック図が載っています。説明のために引用します。

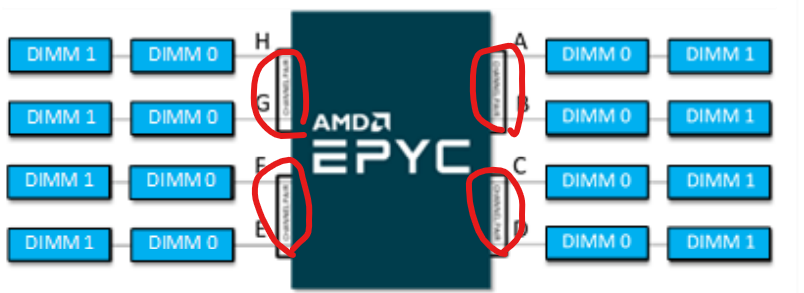

UMC (Unified Memory Controller) が DRAM と一対一で繋がっているように書かれています。

によると、2つのChannelを1組にし、そこのDRAMが繋がっているような図になっています。説明のために引用します。

AMD EPYC ROME のメモリ帯域

下図では、AMD EPYC ROME の STREAM triad の測定データです。説明のために引用します。ピーク値としては、42.x GB/s 出ています。 メモリは 1DPC (DIMM per channel)だと、DDR4-3200が使えるので、転送帯域は 3200MHz x 64bit / 8bit = 25.6GB/s です。42.x GB/s より小さいので、2チャンネルを interleave にして、25.6GB/s x 2 = 51.2 GB/s にして使っているのではないでしょうか?となると、ボトルネックはメモリではなく、他のところになっていそうです。

1CCD => 2CCD にして、ちょこっと10GB/s弱増えているだけなので、この部分がボトルネックではなさそう。となると、GMI2 => UMC の間のパスが 42GB/s 程度になっているのではないでしょうか? 64B/cycle とすると、650MHz、32B/cycle とすると、1.3GHz 程度なんでしょうね。

ちなみに、2023/3/25のブログ、

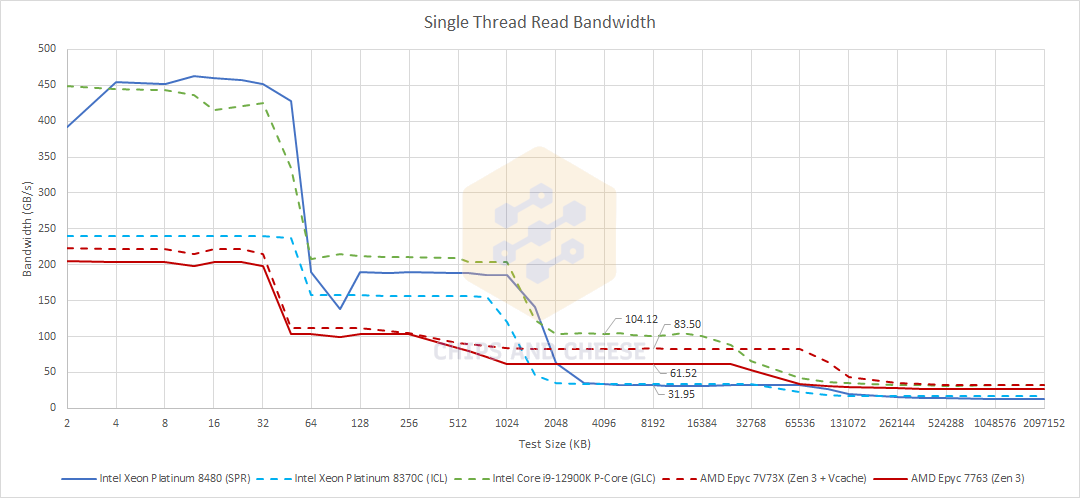

で取り上げたものには、AMD Zen4 or Zen3(Milan) (EPYC 7763) / Zen3 + VCache(Milan-X)(EPYC 7V3X) のbandwidth も載っています。説明のために引用します。こちらは、Single Threadなので、31GB/s 程度のようです。RomeでもSingle Thread では 31.4GB/s です。Rome と Milan/Milan-X では同じ I/O die なので、同じぐらいの転送帯域になっています。

Intel Cascade Lake SP

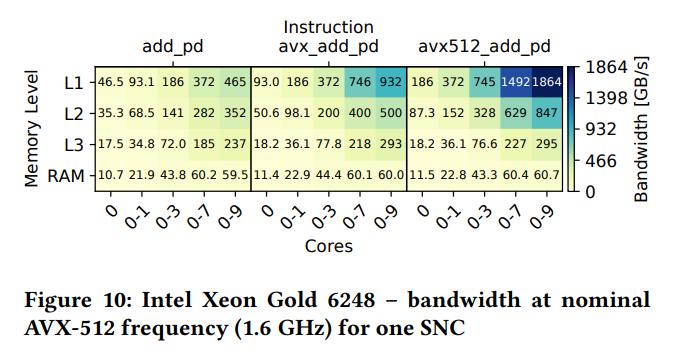

Intel Cascade Lake SPのbandwidth は、下記のようになっています。説明のために引用します。

DRAMのbandwidth は、60GB/s前後のようです。Cascade Lake SPのメモリは、DDR4-2993 なので、23.9GB/s です。メモリコントローラは 3 channel なので、23.9GB/s x 3 = 71.7GB/sになります。71.7GB > 60GB/s なのでメモリコントローラがボトルネックになってなさそうです。となると、Mesh Interconnectが 60GB/s で、64B/cycle だと、1GHz 程度で動いているようです。

おわりに

なんでしょうかね。