はじめに

AMD の EPYC の IOD (I/O Die)から出ている xGMI (Socket to Socket Global Memory Interconnect )。この xGMI を使って、2個の EPYC を接続しています。

今日のブログでは、xGMI について、調べてみました

AMD Rome

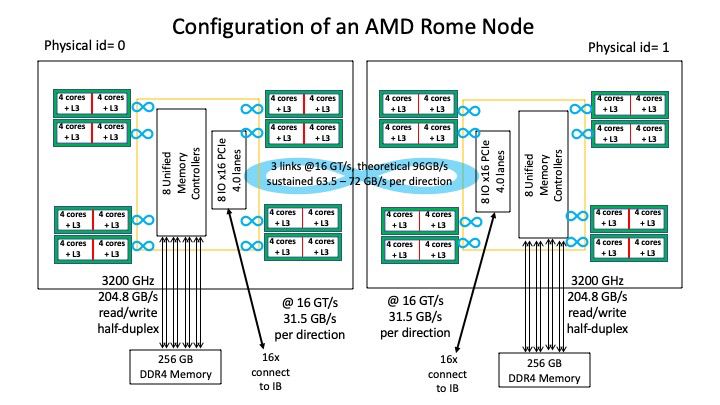

NASAのサイトの下記の資料にあった図(Configuration of an AMD Rome Node)を説明のために引用します。

下図の EPYC 間の説明のところに、

- 3 link @16 GT/s theoretical 96GB/s (sustained 63.5 - 72 GB/s per direction) とあります。この部分が、xGMI になります。

xGMI

上記の記事に、Inter-Socket Interconnect つまり、xGMI のことについて、説明しています。

Inter-Socket Interconnect Two EPYC 7742 SoCs are interconnected via Socket to Socket Global Memory Interconnect (xGMI) links, part of the Infinity Fabric that connects all the components of the SoC together. In each Rome node configured with the HPE Apollo 9000 system architecture, there are 3 xGMI links using a total of 48 PCIe lanes. With the xGMI link speed set at 16 GT/s, the theoretical throughput for each direction is 96 GB/s (3 links x 16 GT/s x 2 bytes/transfer) without factoring in the encoding for xGMI, since there is no publication from AMD available. However, the expected efficiencies are 66–75%, so the sustained bandwidth per direction will be 63.5–72 GB/s.

Note: The xGMI link speed and width can be adjusted via BIOS setting. The xGMI Link Max Speed can be set to 10.667, 13, 16 or 18 GT/s. Setting it to a lower speed can save uncore power that can be used to increase core frequency or reduce overall power. It will also decrease cross-socket bandwidth and increase cross-socket latency. xGMI Dynamic Link Width Management saves power during periods of low socket-to-socket data traffic by reducing the number of active xGMI lanes per link from 16 to 8.

ここには、3 x GMI links using a total of 48 PCIe lanes とあります。つまり、物理レイヤーとしては、48 lanes の PCIe なんですね。つまり、PCIe x 16 が 3組ということです。

Rome間は、3 x xGMI ということがわかりました。Rome の次の Milan/Milan-X も同じですね。

AMD GPU : MI250X の xGMI は?

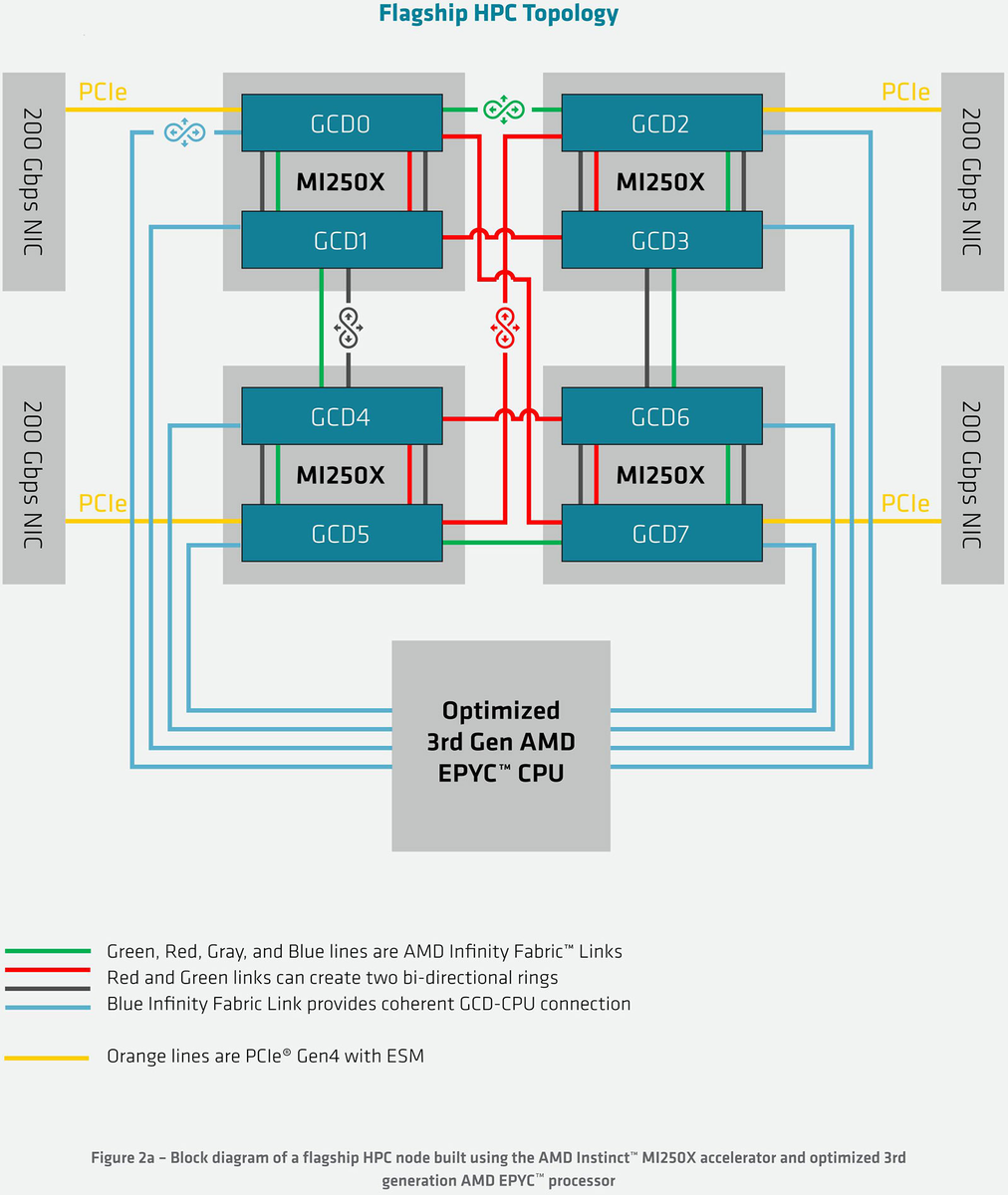

下記の記事の中の図を説明のために引用します。

MI250Xは、2 die で、die 間は 4 x xGMI で接続していますね。各 die から 4 x xGMI、1 package から 8 x xGMIが出ています。その内の 1組が PCIe 4 x16 になります。

PCIe 4 x16 と物理層では同じなんですよね。

ただし、図の黄色の PCIe は、PCIe 4 x16 ではなくて、下記のブログに書いたように、25GT/s なんですよね。PCIe 4 x16 では、16GT/s です。。SERDESは、16Gbps ではなく、25Gbps なんですよね。たぶん。

おわりに

AMD の xGMI は、

The xGMI Link Max Speed can be set to 10.667, 13, 16 or 18 GT/s.

のようです。

プロトコルは PCIe ではなく、キャッシュコーレンシーを保つようになっているんでしょうね。