はじめに

5月28日の下記のブログでは、Ampere ComputingのAmpereOneにもCCIXを持っている?

ということで、CCIX 1.0 の 16Gbps (PCIe Gen4と同じ)ではバランスが悪いので、CCIX 1.1/2.0 ではないのか?と書きました。

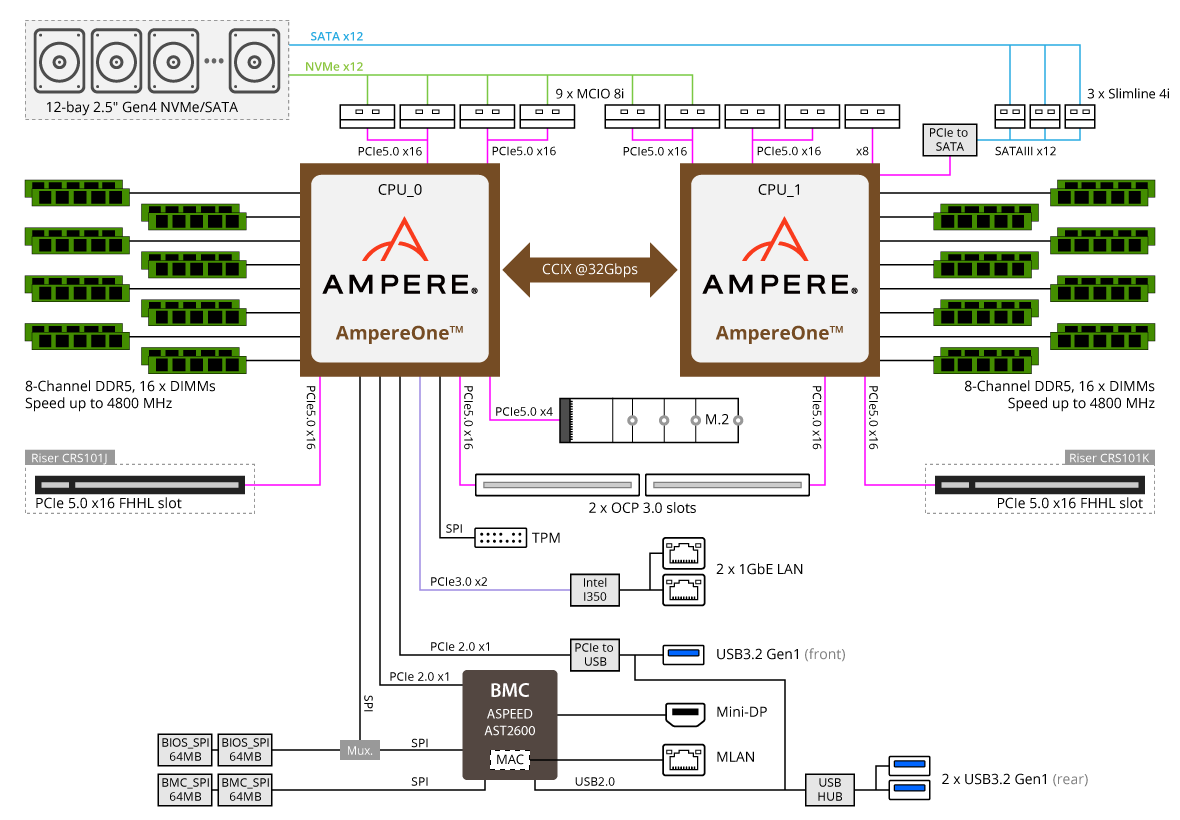

Gigabyte R183-P92

Gigabyte R183-P92 の頁に下記のブロック図が載っていました。説明のために引用します。

このブロック図によると、

CCIX@32Gbps

にて、2ソケット間が接続されていますね。

Ampere Computing の AmpereOne の Prduct Brief にも書いてありました。

128 Lanes PCIe Gen5 (optional 64 lane CCIX for multi-socket support) 32 Controllers Bifurcation to x4

128 Lanes の内、64 Lanes をCCIXで使えると。これは、Altra Maxと同じですね。

Synopsys IP

下記の記事によると、CCIX 1.1/PCIe 5.0 の IP があるようです。

. It leverages PCI Express 4.0 line rates up to 16GT/s with extended speed mode to accelerate speeds up to 25GT/s for CCIX 1.0 as well as 32GT/s for CCIX 1.1. Synopsys is a contributing member of the CCIX Consortium.

とあるので、PCIe Gen5 / CCIX 1.1 の IP を使えばいいみたいですね。

おわりに

Ampere Computingは CCIX 1.0/PCIe Gen5 と Altra/Altra Max の CCIX 1.0/PCIe Gen 4からの互換性を保っていますね。PCIe Gen6 になったら、どうなるのだろうか?

によると、

CCIX Base Specification Rev 2.0 extends CCIX specification Rev 1.2 to support PCIe Gen6 speeds The specification also defines FLIT mode of transportation for CCIX messages for PCIe speeds lower than PCIe Gen6.

とありますね。

の Roadmap を振り返ると、

- 2022 : AmpereOne-1 (5nm)

- 2023 : AmpereOne-2 (5+nm)

- 2024 : AmpereOne-3 (3nm)

- 2025 : AmpereOne-4 (3+nm)

になっているので、CCIX 1.1 は、AmpereOne-1と2、CCIX 2.0は、AmpereOne-3と4になりそうですね。

ちなみに、AMD Genoa も PCIe Gen5 で Infinity Fablic と共通のPHYを使っています。

関連ブログ