はじめに

今回は、AMDのコンシューマ用GPUである、Navi シリーズについて調べてみました。

既に出ている、AMD Navi 21、今年出てくるであろう Navi 31/32/33 についても調べてみました。

Navi 21/22/23

下記のツイートに、Navi 21/22/23 の die shot が載っています。

I fantasy annotated the fantasy die graphic for Navi23, which looks pretty wild in comparison to N21&N22 and remade the one for N22.

— Locuza (@Locuza_) 2021年6月1日

All diagrams above should be correct, Navi23 has 64 ROPs according to AMD.https://t.co/VXmOQfOmFg pic.twitter.com/Gx0m0zXR12

- Navi 21 : Shader Engines (4)、RDNA Workgroups : WGP (40)、GDDR6 256-bit、L3 Cache (64MB + 64MB)

- Navi 22 : Shader Engines (2)、RDNA Workgroups : WGP (20)、GDDR6 192-bit、L3 Cache (48MB + 48MB)

- Navi 23 : Shader Engines (2)、RDNA Workgroups : WGP (16)、GDDR6 128-bit、L3 Cache (16MB + 16MB)

Navi 31/32/33

Navi 31/32/33 については、この記事に詳しく書いてありました。

- Navi 31 : 2 die、Shader Engines (6)、RDNA Workgroups : WGP (60)、GDDR6 256-bit、L3 Cache (512MB)

- Navi 32 : 2 die、Shader Engines (4)、RDNA Workgroups : WGP (40)、GDDR6 196-bit、L3 Cache (384MB)

- Navi 33 : 1 die、Shader Engines (2)、RDNA Workgroups : WGP (20)、GDDR6 128-bit、L3 Cache (128MB + 128MB)

Navi 21/22/23 と比べると、Navi 31/32/33 では、3 vs 2 vs 1 とスケールする感じですね。

それから L3 Cache を増やしています。WGPが40の Navi 21 と Navi 32 を比べると、Navi 21 の 128MBに対して、Navi 32 では 3倍の384MB です。

1 die の NNavi 33 でも 256MB あり、Navi 21の2倍もあります。

一方、メモリコントローラはスケールしていないのは、ピンの制約があるからですかね。

Navi 31 と 32 は、GCD 2 die + MCD 1 die 構成になっていて、GCD内には L3 Cache と GDDR6 がなくて、MCD 内に 搭載しているようです。

GDDR 64-bit あたり、128MB の L3 Cache が付いている感じですね。

NVIDIA Ampere GA102 GPU Architectureのによると、

The memory subsystem of GA102 consists of twelve 32-bit memory controllers (384-bit total). 512 KB of L2 cache is paired with each 32-bit memory controller, for a total of 6144 KB on the full GA102 GPU.

のようなので、メモリコントローラは 32-bit のようです。。となると、64-bit なので、2個のメモリコントローラが付いていることになり、メモリコントローラ当たり、64MB の L3 Cache が付いていることになりますね。

これって、NVIDIA の GA100の全部のL2 Cacheの48MB、GA100の全部のL2 Cacheの60MBよりも多いですね。すごいですよ。

Navi 21/22/23 でも、L3 Cache が 128MB / 64MB / 32MB も載っているんで、AMD は、L3 Cache 大盛が作戦っぽいですね。

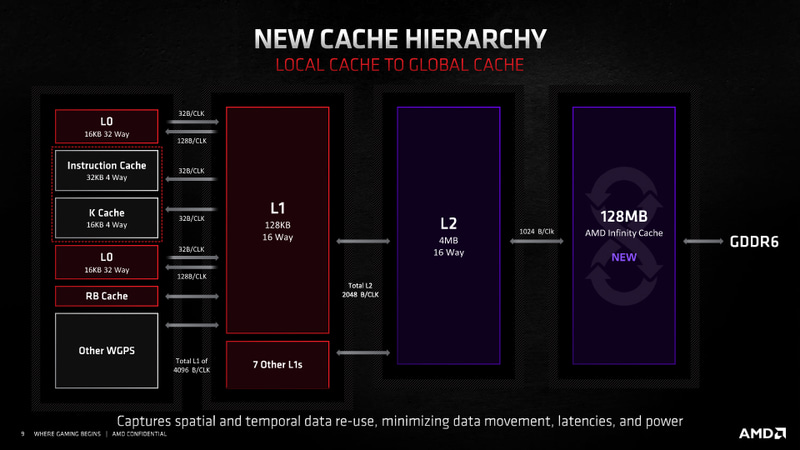

AMD GPU のキャッシュの構成

によると、

Aldebaran (MI200)のCache構成は、

- 16KB : TCP L1 Cahe per CU (num_cu_shared = 1)

- 32KB : Scalar L1 instruction Cache per SoC (num_cu_shared = 2)

- 32KB : Scalar L1 Data Cache per SoC (num_cu_shared = 2)

- 8192KB : L2 Data Cache per GPU (Total Tex Cache) (num_cu_shared = 14)

HPC用のGPUは、L3 Cacheないんですね。

Navi23のCache構成

- 16KB : TCP L1 Cahe per CU (num_cu_shared = 1)

- 32KB : Scalar L1 instruction Cache per SoC (num_cu_shared = 2)

- 16KB : Scalar L1 Data Cache per SoC (num_cu_shared = 2)

- 2048KB : L2 Data Cache per GPU (Total Tex Cache) (num_cu_shared = 8)

- 32x1024KB : L3 Data Cache per GPU (num_cu_shared = 8)

L2は、2MB で、L3は、32MB なんですね。。。

- Navi22 は、L2 (3MB)、L3 (96MB)

- Navi21 は、L2 (4MB)、L3 (128MB)

L3 Cache は、Inifinity Cache

下図は説明のために引用します。

こでRadeonの開発チームが着目したのは、CPUの開発チームで採用されたL3キャッシュであった。サーバー向けのEPYCに採用されているL3キャッシュは、容量32MBでダイサイズはわずか27平方mm。これはRDNAアーキテクチャのL2キャッシュの4倍に相当する容量密度だという。RDNA 2ではこのキャッシュデザインを採用し、GPUとは16×64b/1.94GHz駆動のInfinity Fabricで接続した。

あー、やっと説明を見つけた。やっぱり、CPUにあるL3 CacheをGPUに取り込んだんですね。

おわりに

今回は、AMDの Navi 21/22/23 と Navi 31/32/33 について、調べてみました。