はじめに

NVIDIAのThorについて、調べていたら、面白い資料を見つけたので記録に残します。

- Jetson T5000 and Jetson AGX Orin Series Interface Comparison and Migration

ここにあります。

I/O の比較

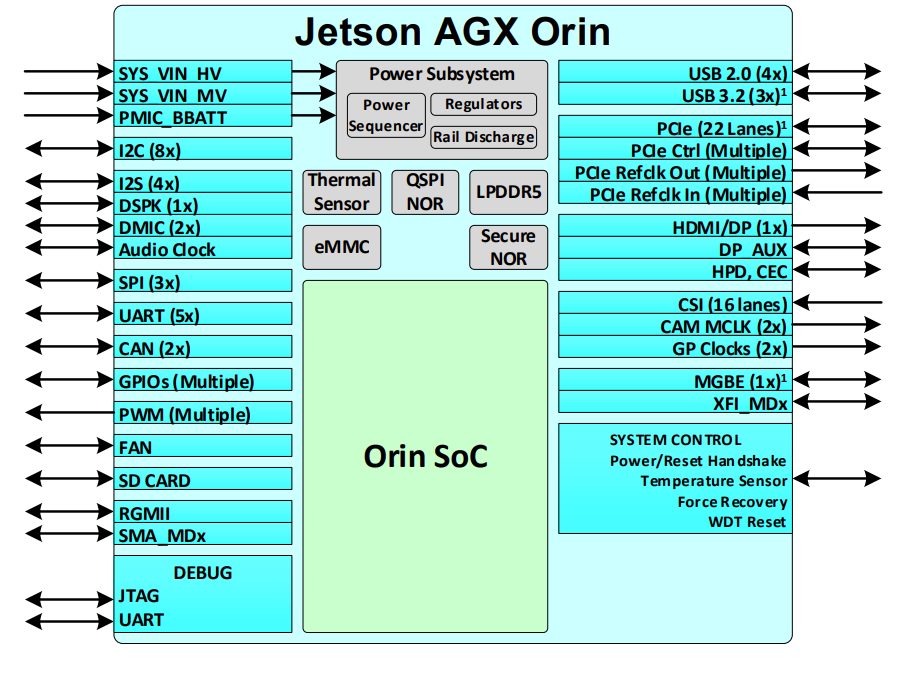

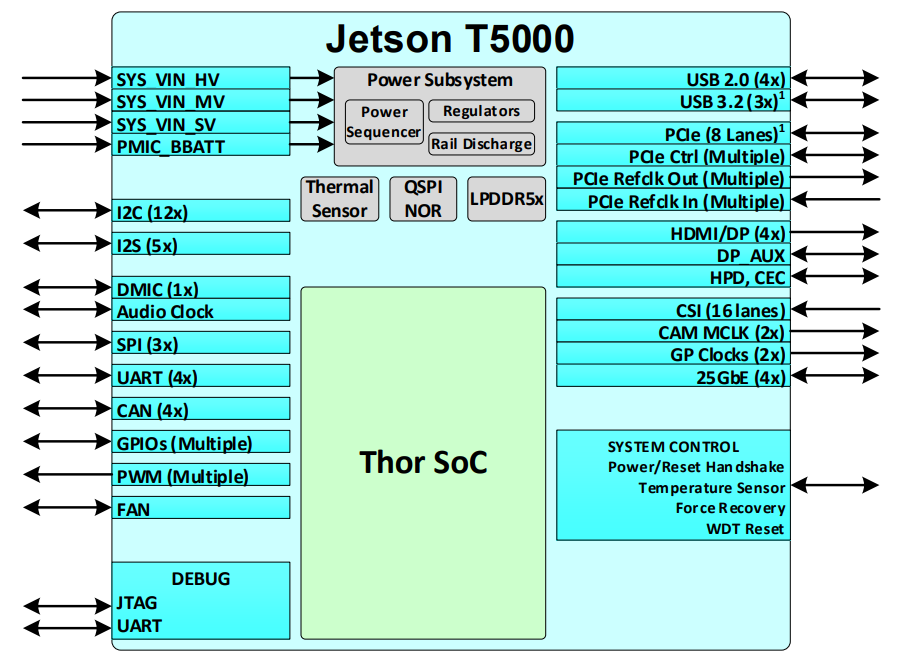

下図は、上記の資料にありました。説明のために引用します。

- I2C : 8 => 12

- I2S : 4 => 5

- UART : 5 => 4

- CAN : 2 => 4

- PCIe : 22 => 8

- HDMI/DP : 1 => 4

- GbE : 10GbE x 1 => 25GbE x 4

PCIe

- PCIe Gen 4: 2 x8, 1 x4, 2 x1

- Only 2 x8 has Endpoint support | 1 lane of 1 x8 shared with MGBE

から

- (up to) GEN5 | Root Port only – C1 (x1) and C3 (x2) | Dual Mode – C4 (x8), C5 (x4), C2 (x1)

- Up to 8 lanes PCIe Gen 5

下記の表に、それぞれのPCIe Configurationが載っています。

Storage

- 64GB eMMC => External Storage (NVMe via PCIe)

これ、NVMe via PCIe なので、上記の PCIe の 8 lane の内、4 lane 使うということ?

上記の図では、Orinには、eMMC が載っていますが、T5000には無いですね。となると、やっぱり、PCIe 経由になるということですかね。

Module Carrier Board

このドキュメントは、SoCとしてのドキュメントではなく、モジュールとしてのドキュメントになるんでしょうね。

もうちょっと調べてみたら、

- NVIDIA Jetson Thor Module Carrier Board

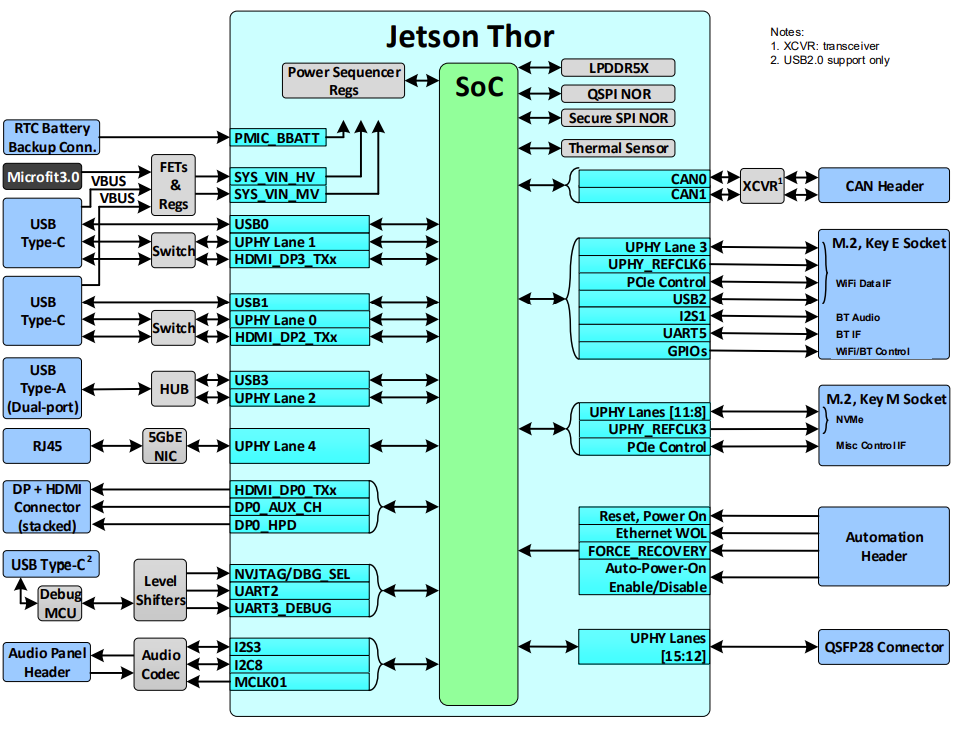

というドキュメントに下図がありました。説明のために引用します。

- M.2 Key E Socket : WIFI/BT 用 (PCIe x 1 : C1, RP)

- M2 Key M Socket : NVMe 用 (UPHY Lanes [11:8]) (UPHY1 : Lane[3:0])

なので、UPHY1 の Lane[3:0] が NVMe 用ですね。。。

PCIe としては、UPHY0 の Lane[7:6] の PCIe x2 (C3), RP ですが、モジュールからは出ていなそうです。

もっと、調べたら、

- Jetson Thor Developer Kit Carrier Board Design Files

の中の

- P4071_A02_OrCAD_schematics(base_version).pdf

の中の下記の図に、UPHY0 の Lane[7:6] が出ているのを確認できました。説明のために引用します。

おわりに

拡張として、PCIe Gen5 x 2 の M.2 Key M Board を1枚させるんですね。