はじめに

AMD EPYC Rome には、WAFL なるものがあり、2ソケットのRome間でこの WAFL を接続しているのを昨日のブログに書きました。

WAFL の実態は、PCIe Gen3 x1 or x2 のようです。PCIe なのでどちらがかMasterになるんでしょうね。

このWAFL って、なんのため?と思って、調べてみました。

どうやら、AMD Infinity Fabric の コントロールファブリックである、制御系の信号を伝達する「Infinity Scalable Control Fabric(SCF)」の役割をしているっぽいです。

Infinity Scalable Control Fabric (SCF)

PC Watch の後藤さんの下記の記事に、Infinity Fabric の説明があります。

Infinity SCFでは電源管理、クロック供給、テスト、初期化、セキュリティといったさまざまな制御のための信号の伝達を行なう。

のようです。

WikiChipのInfinity Fabricにも、SCFの情報がありました。

下記のPC Watchの後藤さんの記事には、Zeppelinアーキテクチャでは、

- CPUパッケージ間を相互接続するIFIS(Infinity Fabric Inter-Socket)は、PCI Expressと共有のPHYを使うマルチプロトコルアーキテクチャとなっている

のIFISを使って、CPU die 間を接続しています。

そして、

ZeppelinのSMUは、ほかのダイやほかのパッケージのSMUと連携する。SMU間の通信は、専用のシングルレーンのIFISを使う。1個のSMUがマスターとなり、スレーブとなるSMUと通信する。

とあり、この部分が SCF に対応しているっぽいです。説明のために下図を引用します。

おわりに

Rome/Milan(Milan-X)のWAFL(実態はPCIe Gen3 x1 or x2) は、Infinity Fabric の Infinity Scalable Control Fabric (SCF) の出入り口になっているのかな?と妄想しています。

WikiChip の Milan の項目では、下記のように書いているので、そうなんだと。

An additional 2-lane PCIe Gen 2 controller powers the WAFL links. One or both of these lanes serve as SCF links between sockets and are otherwise available for I/O, e.g. to attach a BMC.

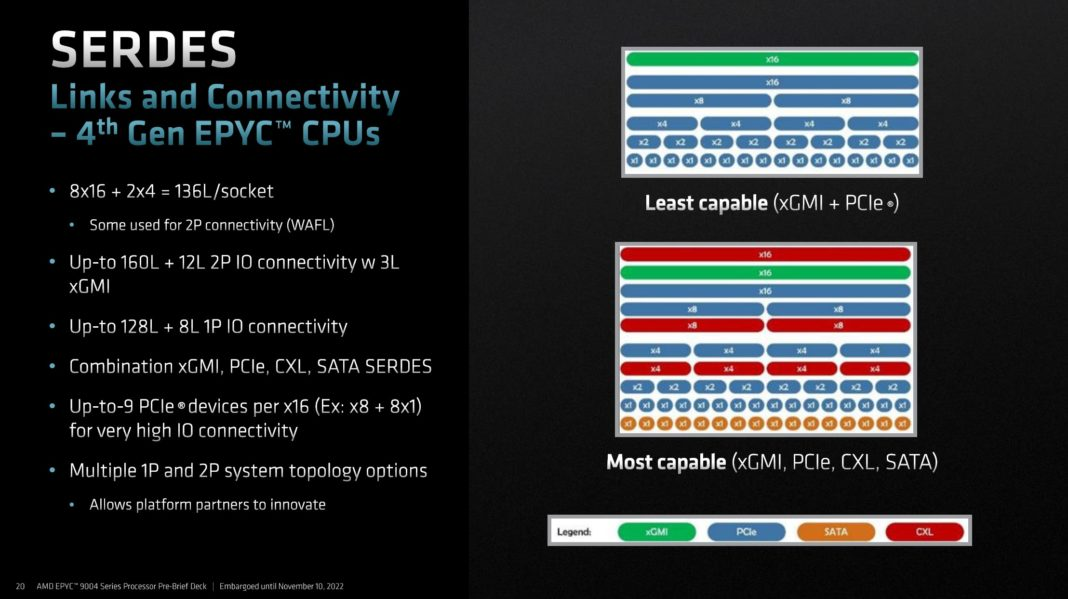

また、上記の記事によると、Genoaでも WAFL はサポートしているようです。下図を説明のために引用します。

下記のツイートと、

My speculation that ROME can support 4S holds since the IF-SCF ring network can be implemented, and 2 x16 IFIS links are sufficient for a "balanced" system. ROME is technically able to support up to 4 sockets. Whether or not AMD chooses to support it officially is another story. pic.twitter.com/YPutoc6d9F

— RetiredEngineer® (@chiakokhua) 2019年4月7日

下記のツイートの左上の画像を説明のために引用します。左上に、2x WAFL Link とあります。これが、SCF x 2 に対応するのだと思います。