はじめに

調べ物をしていて、今更ながら気が付きました。Google TPU v2/v3/v4i/v4 は、HBM2 (HBM2e) ではない。

v2/v3 は、TSMC 16nm で開発。v4i/v4 は TSMC 7nm で開発。

振り返り

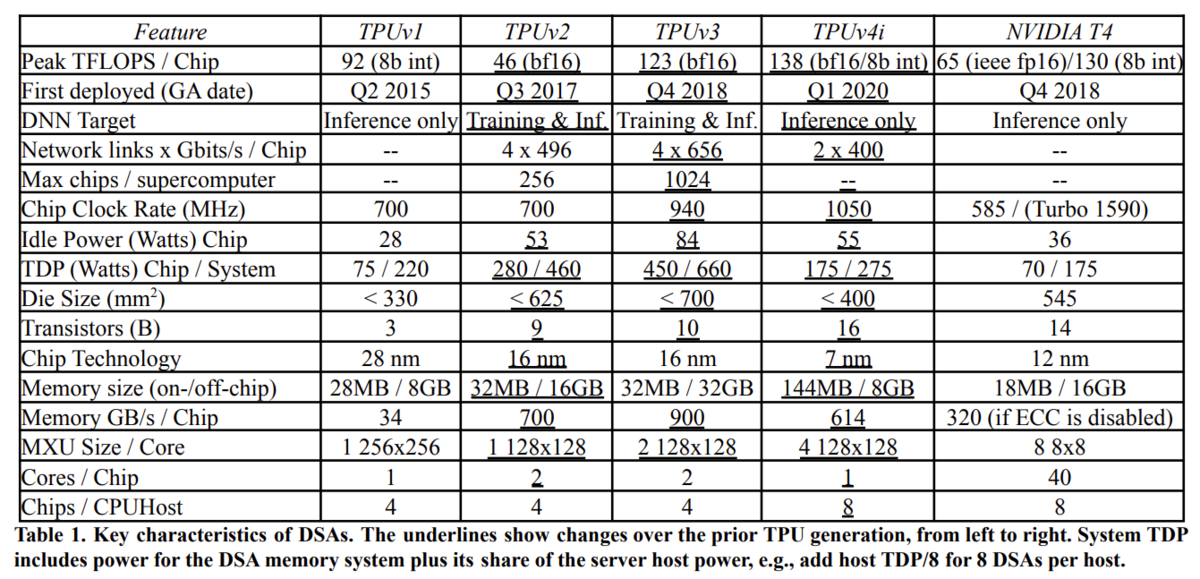

v2/v3/v4i のHBMの帯域は、「Ten Lessons From Three Generations Shaped Google’s TPUv4i」の論文(Table 1.)にて、下記のようになっています。説明のために引用します。

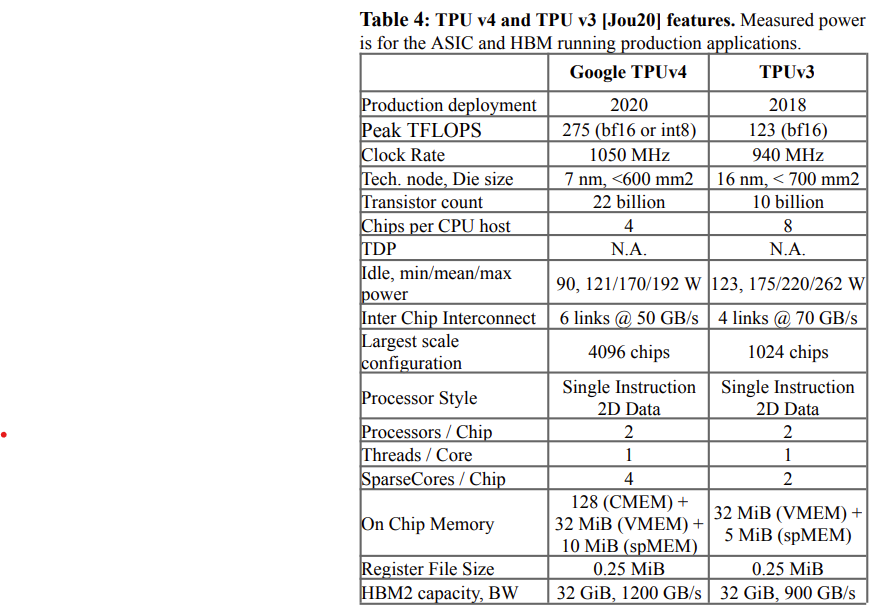

v4 については、TPU v4: An Optically Reconfigurable Supercomputer for Machine Learning with Hardware Support for Embeddingsの論文(Table 4.)にて、下記のようになっています。説明のために引用します。

- v2 : 700GB/s => 4個なので、1つは175GB/s、175 x 8 / 1024bit = 1.367Gbps

- v3 : 900GB/s => 4個なので、1つは225GB/s、225 x 8 / 1024bit = 1.757Gbps

- v4i : 614GB/s => 2個なので、1つは307GB/s、307 x 8 / 1024bit = 2.398Gbps

- v4 : 1200GB/s => 4個なので、1つは300GB/s、300 x 8 / 1024bit = 2.343Gbps

多少、クロックが上がっています。v2 => v3 で 30% up、v3 => v4i/v4 で 33% up

SamsungのHBM2の仕様を見ると、

- 2.0 Gbps

- 2.4 Gbps

があるので、

おわりに

てっきり、TSMC 7nm で開発した v4i/v4 は HBM2e だと思っていましたが、HBM2 でした。v2/v3/v4iv4 の HBM周りの大きな変更をすることがなかったので、HBM2のままだったんでしょうか?