昨日は、VivanteがディープラーニングプロセッサIPに参戦したことを書きましたが、

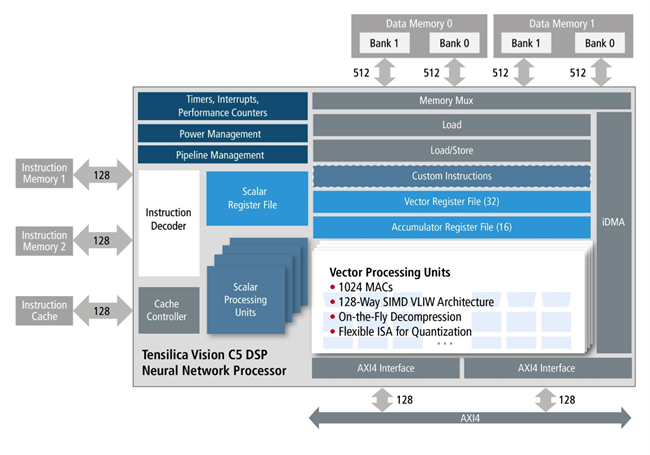

下記の図は、上記のブログから引用しています。

プロセッサには、CNNのアクセレレータは付いていないようですね。

DSPで convolution, fully connected, normalization, poolingなどを処理するようですね。

1024x8bit または 512x16bit のMACができると。

プロセッサには、CNNのアクセレレータは付いていないようですね。

DSPで convolution, fully connected, normalization, poolingなどを処理するようですね。

1024x8bit または 512x16bit のMACができると。

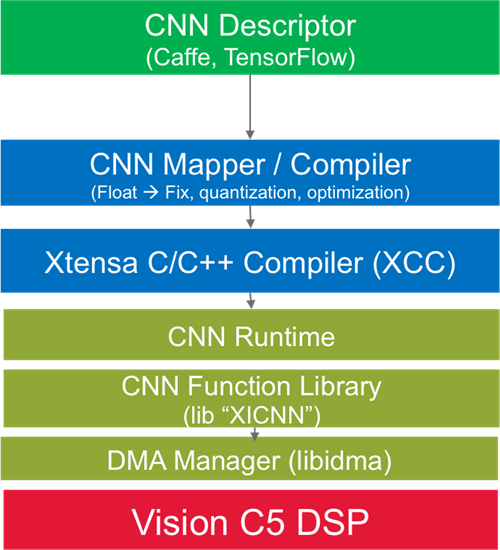

下記の図も同じく引用。

CaffeおよびTensorFlowのモデルからCNN Mapper / Compilerというもので 浮動小数点から固定小数点、量子化、最適化を行い、Xtensa C/C++ CompilerでDSPのコードに変換。

CNN用ランタイムとライブラリ(XICNN)およびDMAマネージャ(libidma)と一緒に動かすと。

CNN用ランタイムとライブラリ(XICNN)およびDMAマネージャ(libidma)と一緒に動かすと。

FPGAのワークフローと似ていますね。

Whiteboard Wednesdays – Introduction to Cadence Tensilica Vision C5 DSPでは、

ホワイトボードを使って、ビデオにて「Vision C5 DSP」について説明してくれますよ。

ホワイトボードを使って、ビデオにて「Vision C5 DSP」について説明してくれますよ。