@Vengineerの戯言 : Twitter

SystemVerilogの世界へようこそ、すべては、SystemC v0.9公開から始まった

Today Xilinx announced Versal Premium, the third series in the Versal ACAP portfolio.

とあるんだけど、

- AI Core Series

- Prime Series

- Premium Series

ということなのかしら?

この他にも、

- AI RF Series

- AI Edge Series

- HBM Series

というのが予定されているっぽい。

Xilinx Versal って、エッジ用だと思っていたが、Versal Premiumは違う。。。

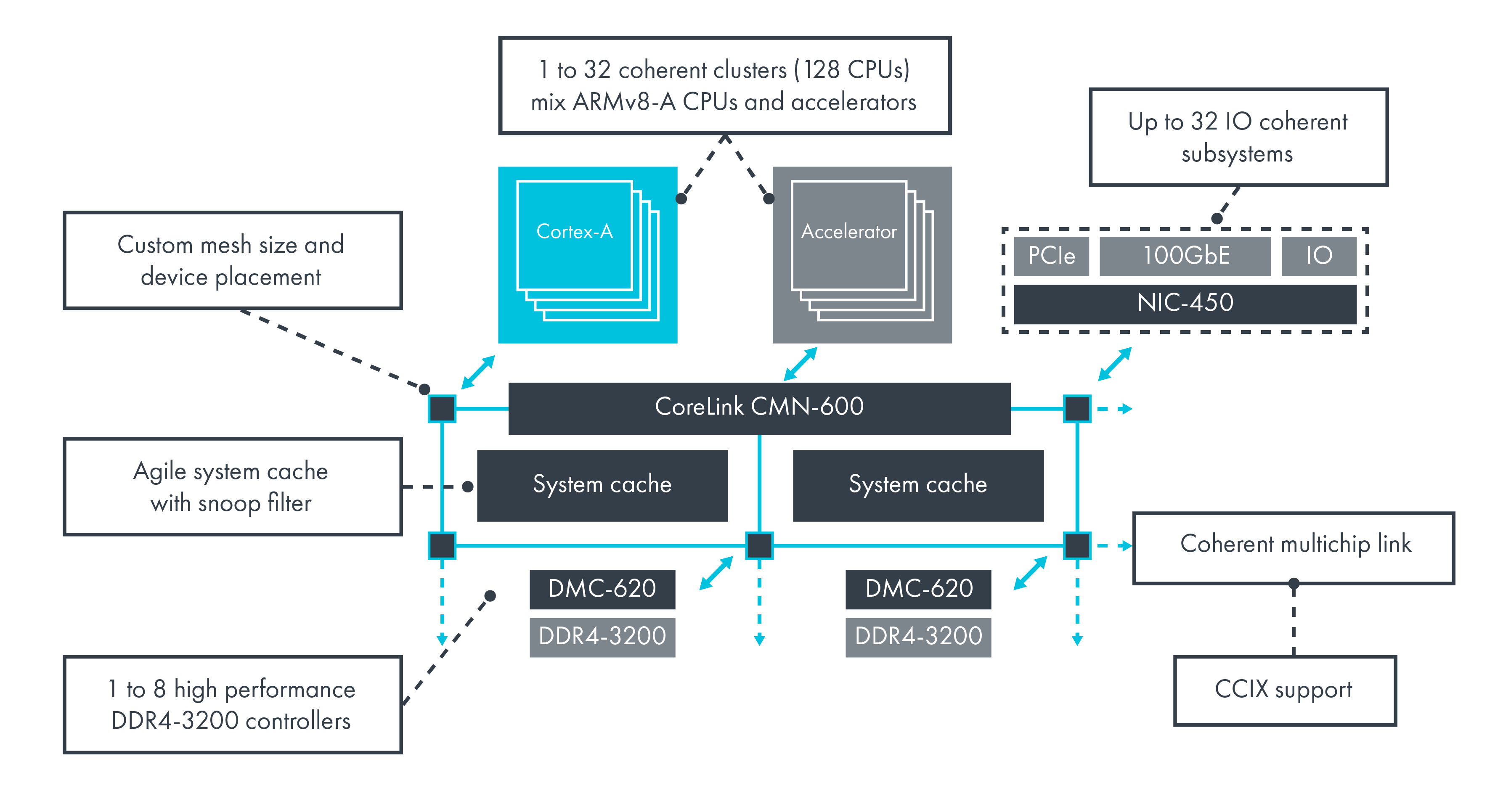

Premium Series は、ここ 。どうやら、PROGRAMMABLE NETWORK ON CHIP というのが、Premiumの特徴なのかしら?

- AI Core Series : CIE & CCIX、DDR、MULTI-RATE ETHERNET、32G、GPIO

- Prime Series : PCIE & CCIX、DDR、MULTI-RATE ETHERNET、32G/58G、GPIO

- Premium Series : PCIE GEN4 W/DMA & CCIX, CXL、DDR4、32G/58G/112G、100G MULTIRATE ETHERNET CORES、600G ETHERNET CORES、600G INTERLAKEN CORES、400G CRYPTO ENGINES、MIPI、LVDS、GPIO

ということに。たしかに、Network & Cloud Accelerator 用だわ。

Prime の VM1502 = AI Core の VC1502

Prime の VM1802 = AI Core の VC1802

Prime の VM2602 = Premium の VP1102

Prime の VM2902 = Premium の VP1402

っぽくて、AI Core == Prime << Premium の規模感

VC1352、VC1502、VC1702、VC1802、VC1902

VM1102、VM1302、VM1402、VM1502、VM1802、VM2502、VM2602、VM2902

VP1102、VP1202、PV1402、VP1502、VP1552、VP1702、VP1802

おまけ

Xilinx Versal AI SoC (VC1502) を4つ繋げたボードを妄想。

— Vengineer@アマゾンプライムで映画三昧 (@Vengineer) 2020年3月13日

DDRx128ビットが8枚なので、PCIe Board の形状は無理。https://t.co/3YqSuBz2sM pic.twitter.com/PFbVJBoUZj