@Vengineerの戯言 : Twitter

SystemVerilogの世界へようこそ、すべては、SystemC v0.9公開から始まった

昨日のAWSの「M6g」インスタンスの Graviton2 は、64コアでしたが、Ampereからのチップは、80コア。動作周波数は、3GHz。

この記事。「Altra」というのがチップ名みたい。Alteraではない。

- 80コア(Arm v8.2 3GHz) + Coherent Mesh Network

- 72bit DDR4-3200 x 8 Channels

- PCIe Gen4 + PCIe Gen4/CCIX (192 lanes)

3GHzのコアということで、A76ですかね。この記事には、7nm で 3GHzとありますね。

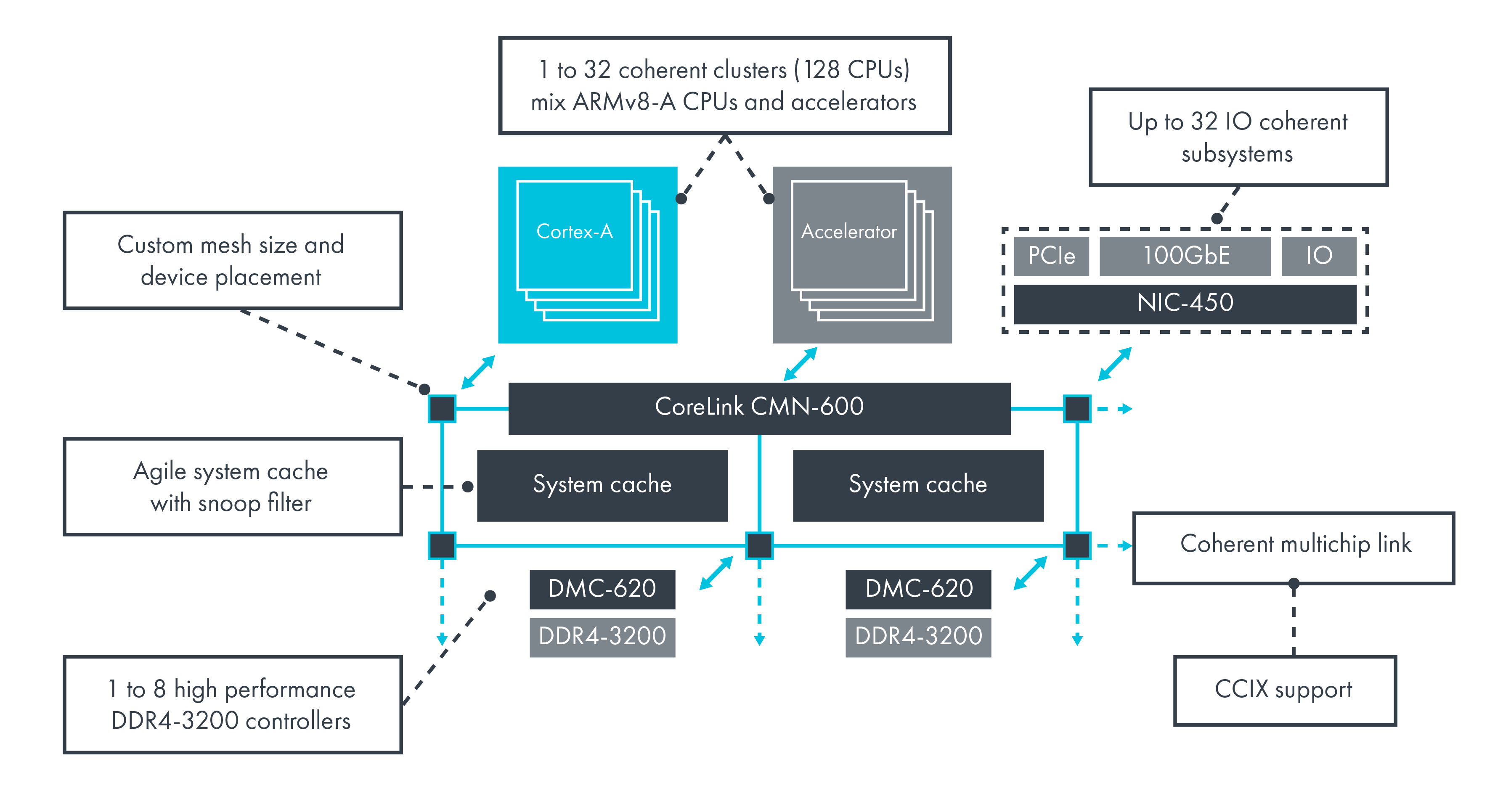

ArmのMesh Interconnect だと、CMN-600ですかね。

追記)、2023.03.13

ここによると、Arm CMN-700 (Mesh Interconnect のようです。

ブロック図はこんな感じ(URLを埋め込んでいます)

メモリは、DDR4-3200対応の DMC-620 。72bitに対応していますね。Chip Selects (per channel)=8 とありますので、たぶん、これですね。8x 2slots = 16 DIMMs。

Coherentmultichip link - CCIX support というのもありますね。

CCIXについては、この資料 の後半に載っていますね。

PCIe Gen4はどこかな?

8 x8 PCIe + 4 x16 PCIe/CCIX

このビデオは、Cadenceだけどね。

2チップ構成の時は、CCIX(x16) を使うのかな? (128 - 1x16x2) x 2 = 192 lanes

追記)、2023.03.13

ここに、CCIX による 2 Socket 間の接続図がありました。説明のために引用します。