はじめに

2014年に一度読んだんだけど、物理本が見つからないのと Kindle 本が半額だったのでぽちり、読み終えました。

詳細

書籍の詳細は、2014年のブログを見ていただければと。

おわりに

成人発達理論。。。

技術的な学習だけでなく、自分の持っている固定概念に対してどう感覚的に学習できるのかが成人になって大切になると。 この固定概念、自分ではわかっていない(無意識)部分もあるので、それについてもしっかり認識するために、この本が役に立つよということでした。

2014年に一度読んだんだけど、物理本が見つからないのと Kindle 本が半額だったのでぽちり、読み終えました。

書籍の詳細は、2014年のブログを見ていただければと。

成人発達理論。。。

技術的な学習だけでなく、自分の持っている固定概念に対してどう感覚的に学習できるのかが成人になって大切になると。 この固定概念、自分ではわかっていない(無意識)部分もあるので、それについてもしっかり認識するために、この本が役に立つよということでした。

TSMCのQ4.2022/2022通期の決算発表を眺めてみましたが、

2023 年はどうなるんでしょうか?

下記のツイートによると、

に対して、

になるようです。

TSMC's N3 (3nm) revenue will reach around $4b in 2023 while N7 (7nm) will see a sharp decline in 2023. N5 will see around 18% growth. N3 revenue will mostly be driven by Apple. $TSM pic.twitter.com/19WUZtOwq2

— Sravan Kundojjala (@SKundojjala) 2023年1月15日

N7以降のプロセスの売上は、$35.1B => $37B と微増ですが、売り上げのトップは N7 から N5 に移り、N3の売上も $4.1B に。

N3の売上は Apple A17 だと思います。

TSMC、2022年の売上はかなり増えましたが、2023年は それほど増えないでしょうが、N7以降を作れるのが Samsung だけなので、それなりなんでしょうね。

Apple A17は、iPhone 15 Proに搭載されると思うので、いつ頃から量産するんでしょうかね。。。

関連記事

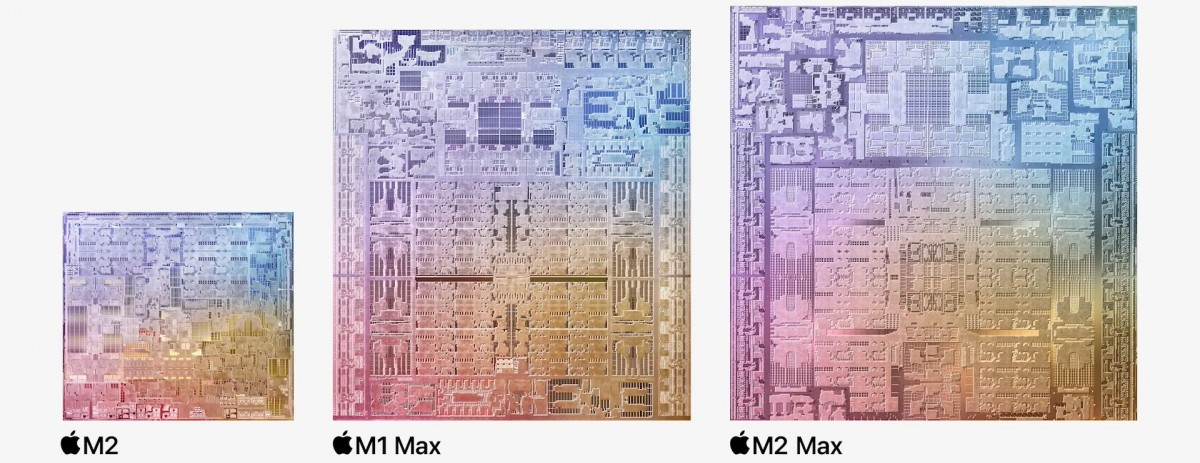

Appleが M2 Pro/M2 Max 搭載の MacBook Pro/Mac Mini を発表しました。

M2 Max/Proの説明のところ、いつもの人じゃないです。

M1 Max/Proの説明の時の人、今まではこの人でした。SVPなので結構偉い人です。

M2 Pro/Max の写真が分かるツイートです。説明のために引用します。

Apple M2 Pro and M2 Max.

— Andreas Schilling 🇺🇦 🇮🇱 (@aschilling) 2023年1月17日

M2 Pro:

- 12 CPU Cores, 19 GPU Cores, 16x Neural Engine

- 40 Billion Transistors

- up to 32 GB of Memory

- 200 GB/s Memory BW

M2 Max:

- 12 CPU Cores, 38 GPU Cores, 16x Neural Engine

- 67 Billion Transistors

- up to 96 GB of Memory

- 400 GB/s Memory BW pic.twitter.com/5UfOTGGuBq

予想では、TSMC N3を使うんじゃないのでは?と言われていましたが、TSMC N3の量産はどうやら2022年12月29日だったようです。

Appleは Mシリーズではなく、Aシリーズが先に出てくるので、AシリーズがTSMC N3になっていないので Mシリーズである M2 Pro/M2 Max が TSMC N3になるのは難しい。また、M2 Max/M2 Pro は M2ベースになるので M2 が TSMC N5Pであるので、TSMC N5Pという結果なんでしょうね。

なんで、TSMC N4Pじゃなくて、TSMC N5Pだったのと?N4Pの量産時期が間に合わないため。

によると、

N4P向けの最初の設計は22年下期にテープアウト(設計完了)の予定である。

とありますので、2023.2.3の販売である M2 Pro/M2 Max にはどう見ても間に合わないですよね。。。

M1 Pro

M1 Max

M2 Pro

M2 Max

大きな差分は、

M1 => M1 Pro/M1 Max で CPU/GPU/Memory を強化したように、M2 => M2 Pro/M2 Max でも CPU/GPU/Memory を強化しました。

Trsは、

Memory帯域は変わらず。M1 Pro/Max は LPDDR5-6400。M2 Proが32GB、M2 Maxが96GB。Proは4個なので1個8GB。8GBは64Gb品。Maxは8個なので1個12GB。12GBは96Gb品。LPDDR5としては128Gb品があるので、16GBx8=128GBまでできそうですが今回は96GBがMax。

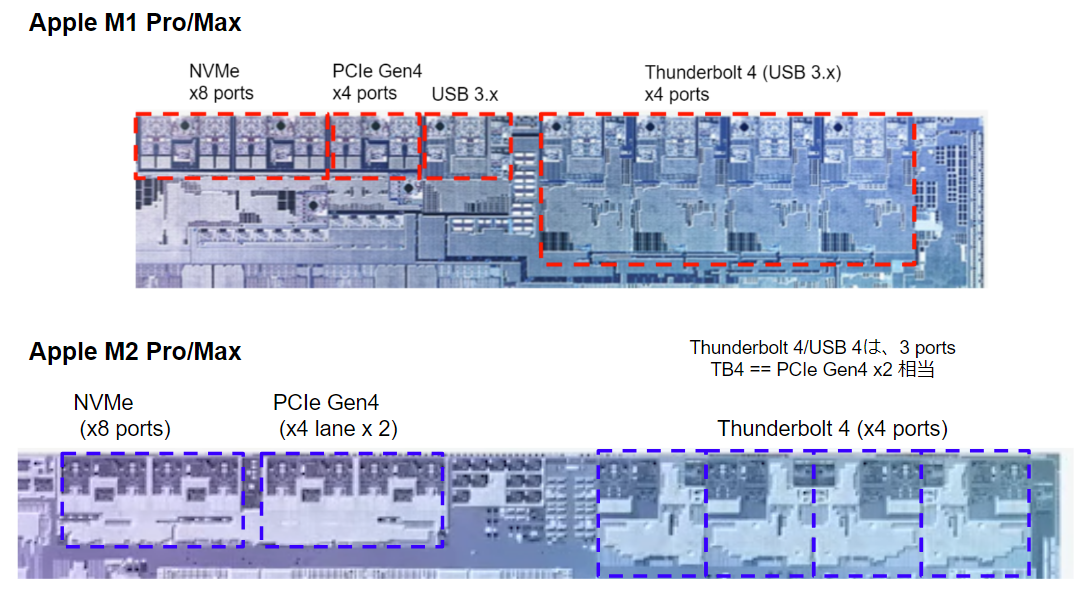

下記の die shot は、Apple unveils M2 Pro and M2 Max: more CPU and GPU cores, more L2 cache, more unified memory から説明のために引用します。

LPDDR5の部分はほとんど変わっていませんね

M1 Max と M2 Max の大きな違いは、M1 Maxでは下の部分に色々なロジックがありますが、M2 Maxではその部分にもGPUコア(3コア)があります。また、真ん中にも3コアあります。+3コアなので、32コア => 38コアになります。

M1 Proの下の部分がカットされている写真ですが、どうみても、M2 Pro も下の部分がカットされている感じです。なので、M2 Ultraが出てくるのは確実です。

PCIe/Thunderbolt 4の部分。大きな変更はなさそうです。SSD、M1 Max/Pro では、512GB/1T/2TB/4TB/8TB。M2 Max/Pro でも同じです。

Mac Mini (M2 Pro) : Thunderbolt 4 x 4 + HDMI + USB-Aポート(最大5Gb/s)x2 + 1GbE(10GbE) + Wifi 6E/Bluetooth 5.3 + SSD (512GB/1T/2TB/4TB/8TB)

M1 Ultra の Mac Studio は下記のような感じになっていたので、M2 Pro/Max の MacBook Pro も基本的には同じなんでしょうね。

M1 => M1 Max/Pro の間が 1年。M2 => M2 Max/Pro が 7か月。。。なんでこんなに短いのだろうか。。。

M1搭載のMac miniは2020/11/17発売。M2搭載のMac miniが2023/2/3発売。

次は、iPhone 15用のA17。これはTSMC N3でしょうね。A16 => M2 になっているので、A17 => M3 => M3 Max/Pro の流れになりそうです。

2027年までは予測できそうです。。。

Apple M2 Pro/Max がこの時期に発表になったのは、

— Vengineer@ (@Vengineer) 2023年1月18日

今年景気後退が起こる可能性が高いので早いところ売っちゃえ作戦なのかな?

本来なら6月頃発表だと思うんだけどね。。。

どうなんだろうか?

関連ツイート

下記のツイートの内容は、プロセス的に早過ぎるという返信もありますね。

(1/2)

— 郭明錤 (Ming-Chi Kuo) (@mingchikuo) 2023年1月17日

I expect the next new MacBook Pro models, which will adopt M3 Pro/M3 Max processors made by 3nm (likely TSMC's N3P or N3S), will go to mass production in 1H24. https://t.co/8JR4LOHFVs

参考

Google Tensor G1/G2用の Android 13 の kernel を眺めていたら、Trustyなるデバイスドライバを見つけました。Linuxのdriversの下には trusty は無いので Android 独自なのかな?と思っていました。

色々とGoogle君に聞いたら、下記のGoogle Blogを見つけました。この中で、Google Tensor G1 (Pixel 6 & Android 12) にて、Private Compute Core/Arm TrustZone/Trusty OS/Tensor Security Coreというものを導入したようです。

下図は上のブログにあるものです。説明のために引用します。

通常は、Android OS が Tensor SoC (G1/G2) の中の Main Application Processor (Cortex-X1/A76/A55) にて動いています。これに、

が追加された感じです。

Trusty は、ここ に説明があります。下図は、Trustyのサイトから説明のために引用します。

Trusty そのものは、ここ にあります。

Arm版だけでなく、Intel版は Intel のサイトにあります。

どうらや、gsa というデバイスドライバが関係しているっぽい。Kconfig の 中で pKVM が使われている。

config GSA

tristate "GSA driver"

default n

config GSA_PKVM

bool "Support pKVM"

depends on GSA

depends on PKVM_S2MPU

default n

config GSA_GSC

tristate "GSC Proxy"

depends on GSA

default n

gsa_tz.c では、TrustZone へのアクセスをしている。また、trusty のコードもあります。

#include <linux/trusty/trusty_ipc.h>

このコードの中で、trusty なるものがある。

#define HWMGR_TPU_PORT "com.android.trusty.gsa.hwmgr.tpu" #define HWMGR_AOC_PORT "com.android.trusty.gsa.hwmgr.aoc"

Google Tensor G2 の Edge TPU のデバイスドライバからわかったこと!(その5)

Google Tensor G1 と G2 の debug 用 コードは、ここにあります。

この2つの内容の違いは、gs201-itmon.c に、AUR0/AUR1 というキーワードがあるということ。この AUR0/AUR1 は、GXP (DSP) に関係するっぽい。つまり、DSP の codename の Aurora から来ていると。

gs201-gxp.dtsi に下記のようなエントリがあります。

reg-names = "aur",

"mailbox0", "mailbox1", "mailbox2", "mailbox3",

"ssmt_idma", "ssmt_inst_data";

interrupts = <GIC_SPI IRQ_MAILBOX_AUR02AP_ALIVE IRQ_TYPE_LEVEL_HIGH

GIC_SPI IRQ_MAILBOX_AUR12AP_ALIVE IRQ_TYPE_LEVEL_HIGH

GIC_SPI IRQ_MAILBOX_AUR22AP_ALIVE IRQ_TYPE_LEVEL_HIGH

GIC_SPI IRQ_MAILBOX_AUR32AP_ALIVE IRQ_TYPE_LEVEL_HIGH

GIC_SPI IRQ_AUR_WDOG_CPU_IRQ_AUR IRQ_TYPE_EDGE_RISING>;

tpu-device = <&edgetpu>;

gsa-device = <&gsa>;

gxp-tpu-mbx-offset = <0x0 0xC0000>;

iommus = <&sysmmu_aur_idma>, <&sysmmu_aur_inst_data>;

samsung,iommu-group = <&iommu_group_aur>;

reg-names に "aur" があり、iommus に、sysmmu_aur_idma と sysmmu_aur_inst_data の2つがあるので、DMAが2つあることを意味します。割り込み関連が GIC_SPI IRQ_AUR_WDOG_CPU_IRQ_AUR IRQ_TYPE_EDGE_RISINGになります。

また、

にありました

#define EDGETPU_NUM_EXT_DSP_MAILBOXES 4

の 4つの mailbox に関するものが、

"mailbox0", "mailbox1", "mailbox2", "mailbox3",

がレジスタ、

interrupts = <GIC_SPI IRQ_MAILBOX_AUR02AP_ALIVE IRQ_TYPE_LEVEL_HIGH

GIC_SPI IRQ_MAILBOX_AUR12AP_ALIVE IRQ_TYPE_LEVEL_HIGH

GIC_SPI IRQ_MAILBOX_AUR22AP_ALIVE IRQ_TYPE_LEVEL_HIGH

GIC_SPI IRQ_MAILBOX_AUR32AP_ALIVE IRQ_TYPE_LEVEL_HIGH

が割り込みになるようです。

AUR0/AUR1 は、DSP (codenameがAurora) だということがわかりました。

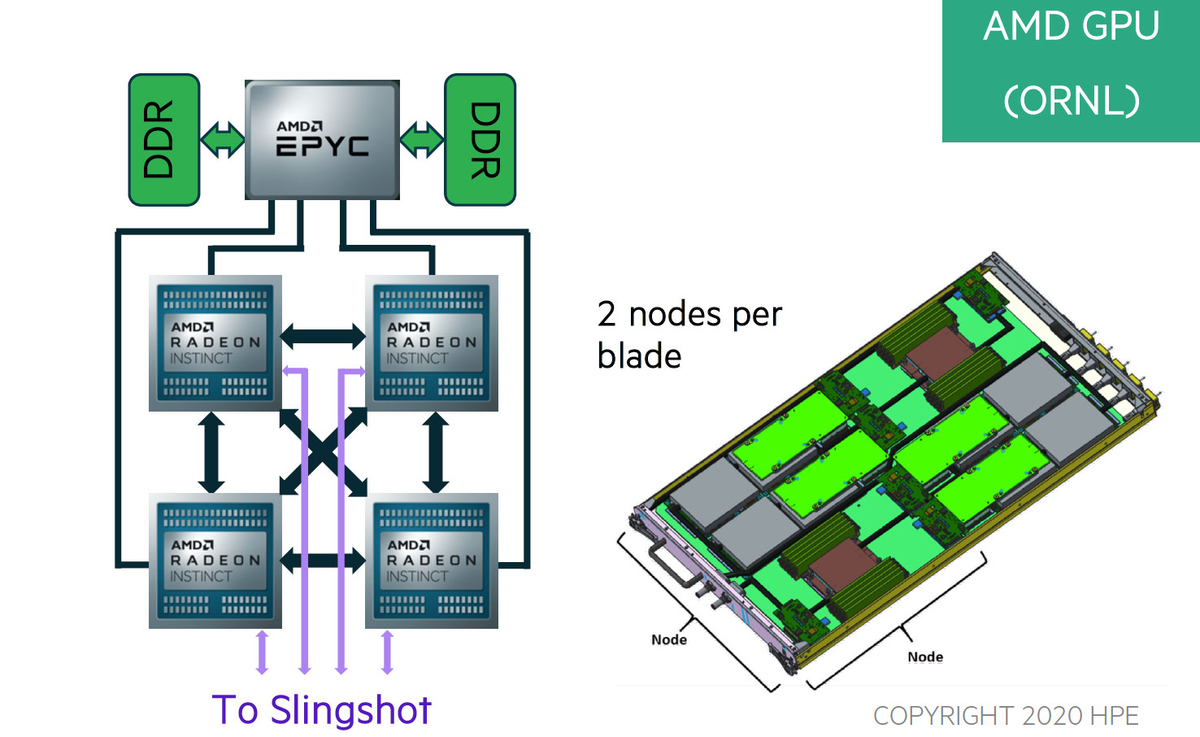

先週の CES 2023 での AMD講演の最後に、MI300の発表がありました。

MI300 に関しては、既に色々な人がまとめてくれているので、そこを引用することとします。

下記は、tom's HARDWAREの記事です。

チップのアップ写真が載っています。

CES 2023の時に、

と言っています。これに、8個の HBM3 chip が載っています。写真では、4個のchip、8個のHBM3、8個のchip は認識できたのですが、残りの1個は分かりません。

4個の 5nm chip に関しては、どうやら

のようです。

各 chip に 32GB の HBM3 のみなので、EPYCの1TB/1.5TBのDDR4/DDR5に比べてかなり少ないので、どこかにDDR系のメモリを接続するための仕組みはあると思います。

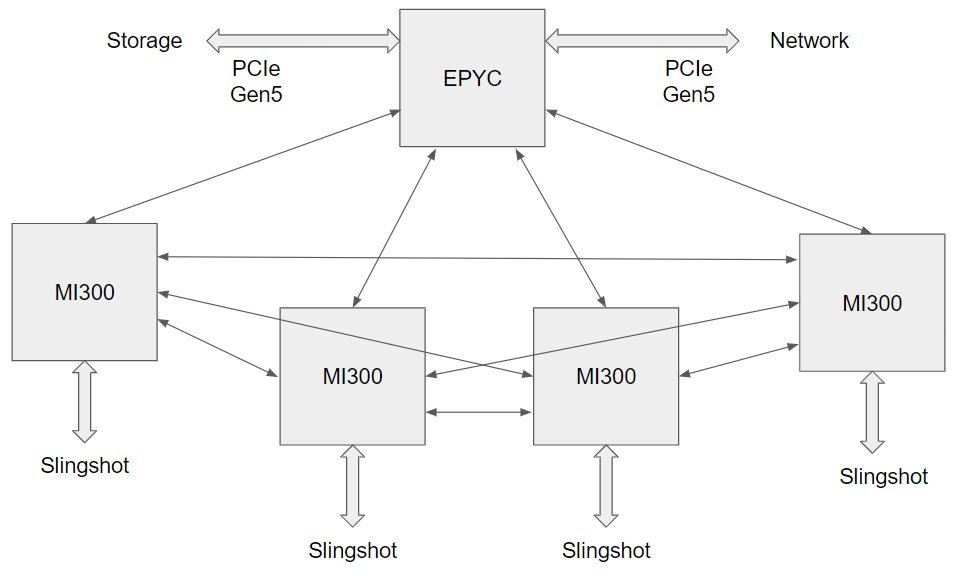

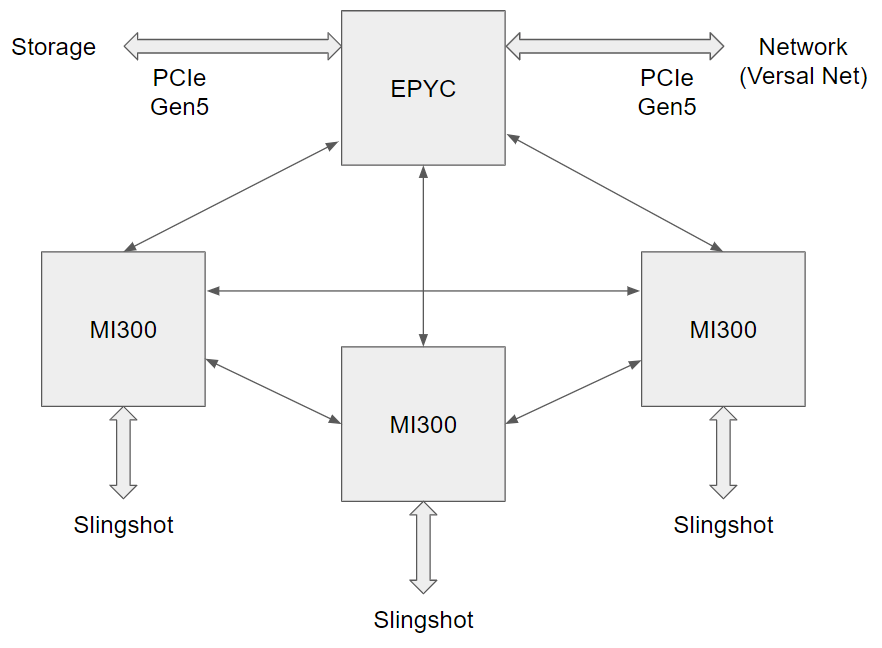

MI250X搭載のFrontierのノードの構成は下記のようになっているようです。下図は、AMD TEASES DETAILS ON FUTURE MI300 HYBRID COMPUTE ENGINESから説明のために引用します。

1個のCPU(EPYC) + 4個のGPU(MI250X)

CPUコア数は64個。MI250Xの中身は 2 dieなので、1 die あたり 8コア

一方、MI300 の CPUコア数は24個。GPUのdie数は3。1 die あたり8コアになるので、Frontier の割合と同じ。

また、MI250Xでは 1 die あたり HBM2e (3.2Gbps) x 4 で、MI300 では 1 die あたり HBM3 (6.4Gbps) x 2 でメモリ帯域も同じ。

というところから、下記のような構成のノードを妄想しましたが、GPU側のNetworkであるSlingshotが3つとなるので、

やっぱり、MI300は4つになるのかな?と。ただし、ホストとなるEPYCは64コアとかじゃなくて、もっと軽いものになるんじゃないですかね。

2022年までは x86-64をホストにAccelarator を付けるという構成だったのが、2023年からはAI/ML用のコンピュータというものが出てくる感じですね。

Data Center の売上トップ3が、CPU、GPUの個別プロダクトだけでなく、CPU+GPU の統合プロダクトをアナウンス。

2023年、Data Centerは新しい方向性の幕開けになるのでしょうか?

関連記事

先週の金曜日にAMDがCES2023にて、Xilinx の AI Engine を投入した Ryzen 7040 を発表しました

Ryzen AI Engine

下図は上記のビデオから説明のために引用します。

4つのストリーム処理ができるの?

March 2023 にPCに搭載されたものが出てくるようです。

AI Engine って、Versal AI Engine と同じようですが、プログラミングも同じようにするのでしょうかね。。。

Intel は、第13世代 Core では、Mobileye VPU を M.2 で接続し、第14世代 Core では Chip ないに取り込むようです。