@Vengineerの戯言 : Twitter

SystemVerilogの世界へようこそ、すべては、SystemC v0.9公開から始まった

はじめに

このブログで RISV-V を取り上げたのは 2014年8月20日のこちら

vengineer.hatenablog.com

この時のブログでは、「ARMがCPUの世界の主流になろうとしている」と書いている。

ARMはこの後、SoftBankに買収され、それをNVIDIAに転売した。

6年半の歳月が流れ、やっと、RasPiに対抗できそうなRISC-Vボードが「BeagleV」が出ます。

Beagle Boardは、ガジェット用ボードとして、一時期ブームになりましたが、

その後、RasPiに持っていかれてしまいました。

BeagleV

BeagleV は、StarFiveのSoC(StarFive JH7100)を搭載したボード。

公式サイトは、

https://beaglev.seeed.cc/

下記の写真は、組み込みURLで取り込んでいます。

https://beaglev.seeed.cc/img/s2-tips.png

見た目には、普通のボードです。

StaFiveは中国のFablessの会社のようです。サイトを覗いてみたら、SiFiveのCPUコアを中心等したSoC開発サポートって感じです。

そのStarFiveが開発したSoC(StarFive JH7100)の情報のこのサイトにはありませんでした。

SoC

メモリとストレージ

- LPDDR4 4GB x 2 (最大 : 8GB)

外部インターフェース

価格

- 4GB : 119ドル

- 8GB : 149ドル

リリース時期

- 2021 April : Pilot Run For Community

SiFive RISC-V U74 Core

SiFive の U74 のサイトは、こちら。マニュアルは、こちら。

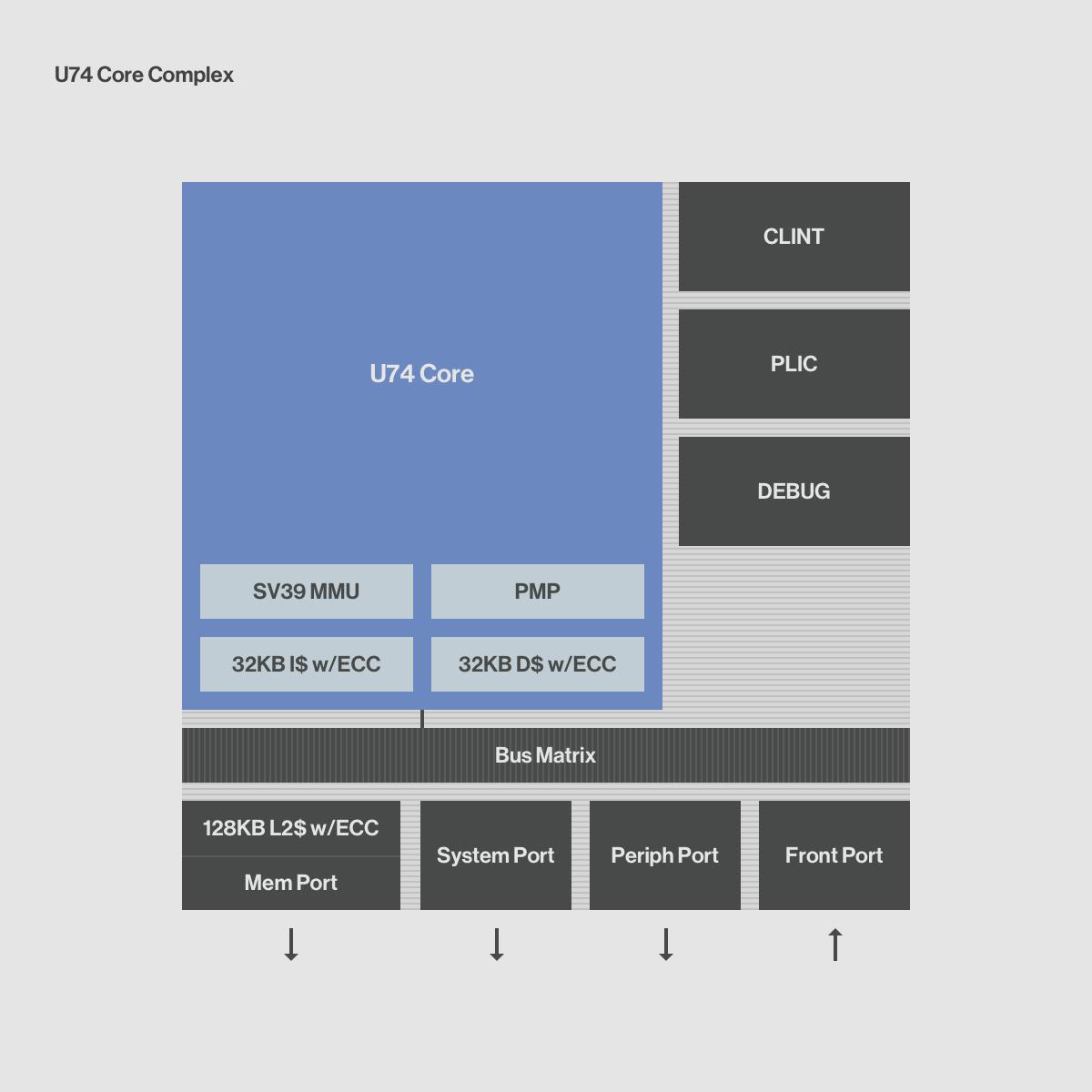

下図は組み込みURLで引用しています。

L1Cache は、I/D共に32KB。MMUも付いています。L2 Cacheは内部のBus Matrix経由でのアクセスになっています。

Dual Coreなので、どうやって、L2 Cache に接続しているのでしょうかね。

関連情報

日本語の解説:たった1万円台のRISC-V CPU搭載&Linuxの動作に対応したお手頃コンピューターボード「BeagleV」

gigazine.net