はじめに

TTenstorrent は、RISC-Vコアを128個搭載した AEGIS CPU chiplet を発表

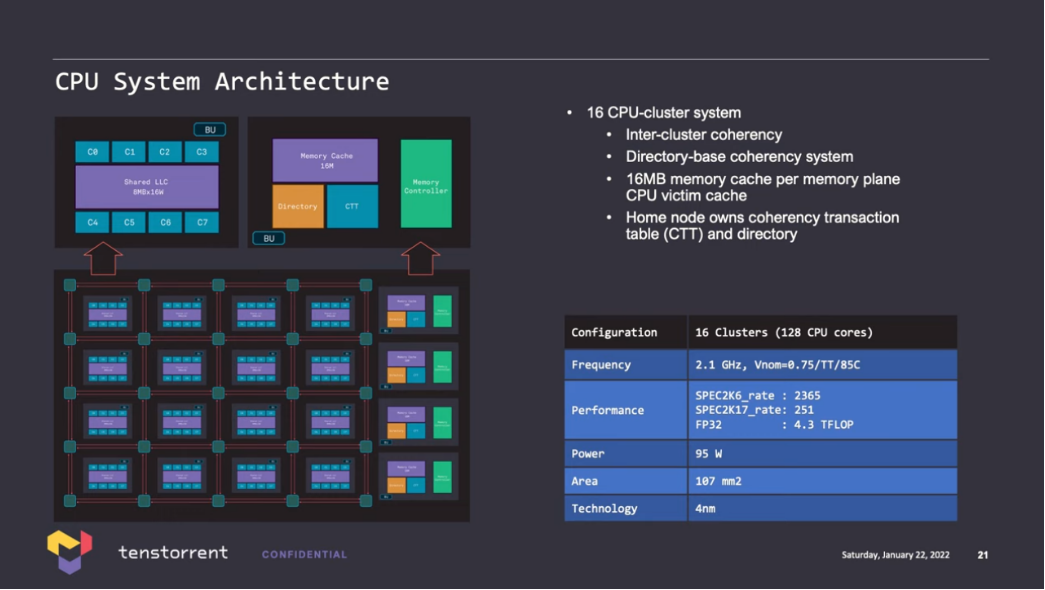

下記の図は、上記のYoutubeから説明のために引用します。

AEGIS とは?

下記が AEGIS Chiplet System Architecture のブロック図です。

4つのNUMAで、各NUMAでは32コアのRISC-Vコアがあります。AMDのEPYCやIntelのSapphire Rapidsみたいな感じですね。

各NUMAの32コアは、4つのブロックに分かれていて、各ブロックにAscalon Clusterと呼ばれているようです。

- 8 Core/per Cluster

- 230GB/S CHI coherency bus

- 230GB/S AXI message passing bus

- 12MB shaed cluster cache

Software and Silicon in Serbia w/ Ljubisa Bajic and Jim Keller では、

模様なスライドを公開していました。

- TSMC 4nm

- 16 CPU-cluster system : 128 Cores

- 2.1 GHz, Vnom=0.75/TT/85C

- Power : 95W

- Area : 107mm2 (4nm)

die size が小さいです。Apple M1 (TSMC 5nm) が 119mm2 ですので、それよりもちょこっと小さいです。M1のCPUコアは、big x 4 が 3.2GHz、little x 4 が 2.064GHz です。

Ageis Server

AEGIS CPU chiplets をベースに、DDR chiplets, I/O chiplets, Accelerator chiplets にて、サーバーを構築するというものです。

- 下図の左側は、DDR5 chiplet を6個使用したケース

- 下図の右側は、HBM chiplets を4個利用したケース

のようです。

おわりに

AEGIS CPU chiplets + DDR5 chiplet + I/O chipltes に、Blackhole (TSMC 6nm) を接続した RISC-V ベースのAI Computer の構築もできそうです。

x86-64無しでシステムとしては、

- NVIDIA : Grace-Hopper Superchip

がありますが、RISC-Vで構築とは、とてもチャレンジですね。