@Vengineerの戯言 : Twitter SystemVerilogの世界へようこそ、すべては、SystemC v0.9公開から始まった

はじめに

Twitter の TLで拾った下記の記事。

L1 Instruction plus Cache がある

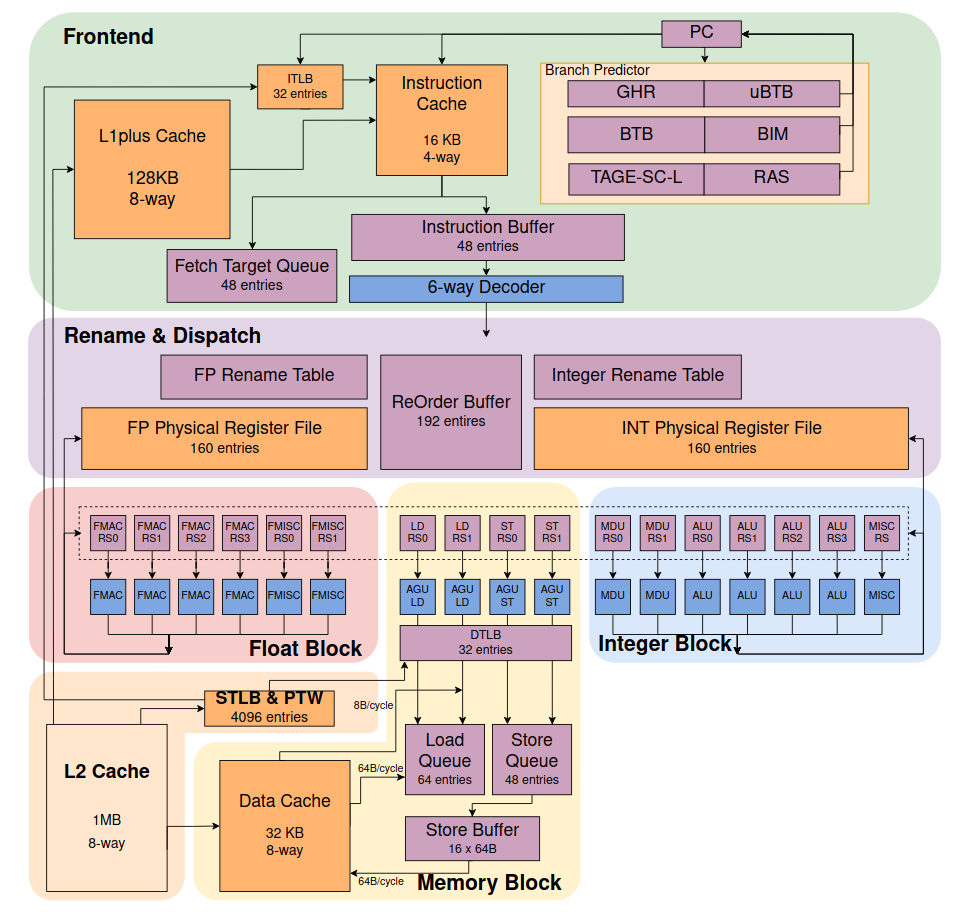

上記の記事の中にあったXiangShan open-source processor のブロック図。説明のために引用します。

- L1-I cache 16KB, 4way,

- L1-I plus cache 128KB, 8way,

- L1-D cache 32KB, 8way,

- L2 cache 1MB, 8way

L1 Instruction Cache は少なめの 16KB, 4way ですが、L1 plus Cache として、128KB 8-way なるものがあります。 4way でかつ高速アクセスできるが容量が少ない16KBものと、8wayだけど128KBと容量がそれなりのL1 plus という2段構成。その下に、L2 Cache 1MB, 8way があります。

128KBのL1って、AppleのA/MシリーズのCPUコアのものと同じですよ。

Chisel

どうやら、このコア、Chisel で開発しているようです。 20218年のFPGA(xc7v2000tfhg1716-1)に実装したら、Verilog HDLのものと同等レベルの性能が出て、チューニングをした Chisel ではよりよくなったようです。 2020年にはChisel で記述されたコアを 8コア を TSMC 28nm で実装したものもあります。

ソースコード

確かに、L1plusCache.scale もありました。

VCS と verilator でシミュレーションできるようです。

ドキュメント

ドキュメントも 中国語ですが、github.com にて公開されています。