はじめに

AMD CDNA (サーバー用GPGPU)のメモリコントローラの部分を調べてみたら、気が付きました。

MI200 の メモリコントローラは、8チャネル?

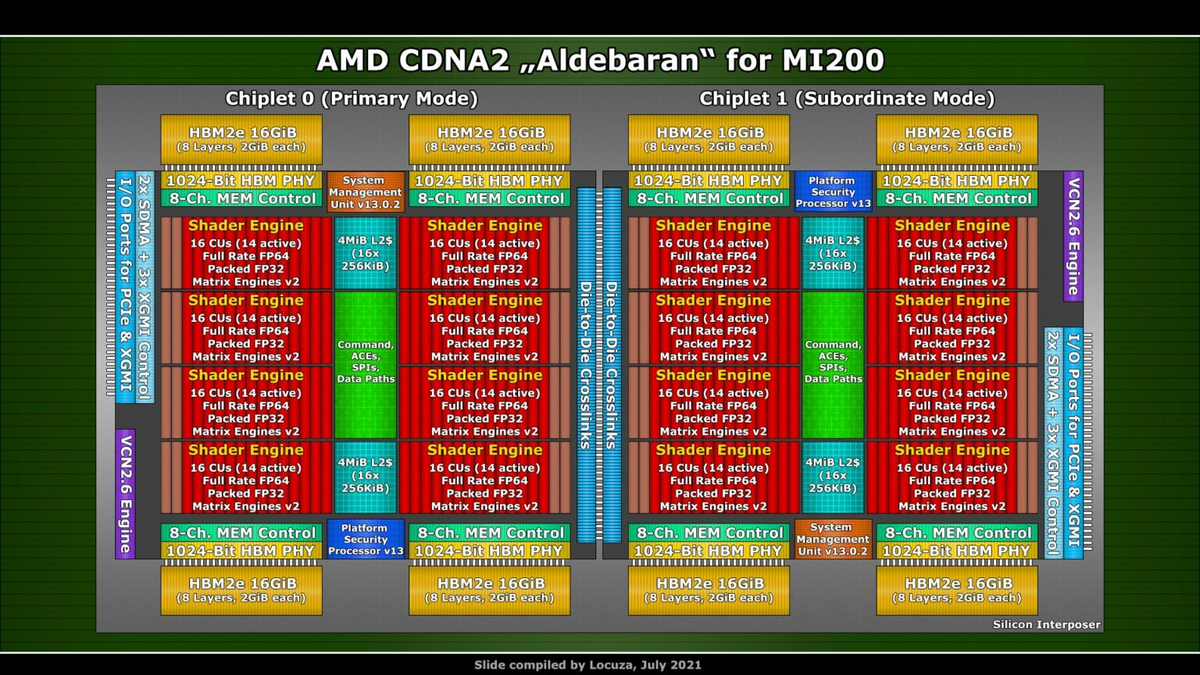

下記の記事の中にある図に、MI250の/MI250Xメモリコントローラは 8-ch という文字がありました。下図を説明のために引用します。

1 die には、4個のHBM2eメモリが接続し、その手前のメモリコントローラは 8-ch だと。

CNDA/CDNA 2 の Whitepaper

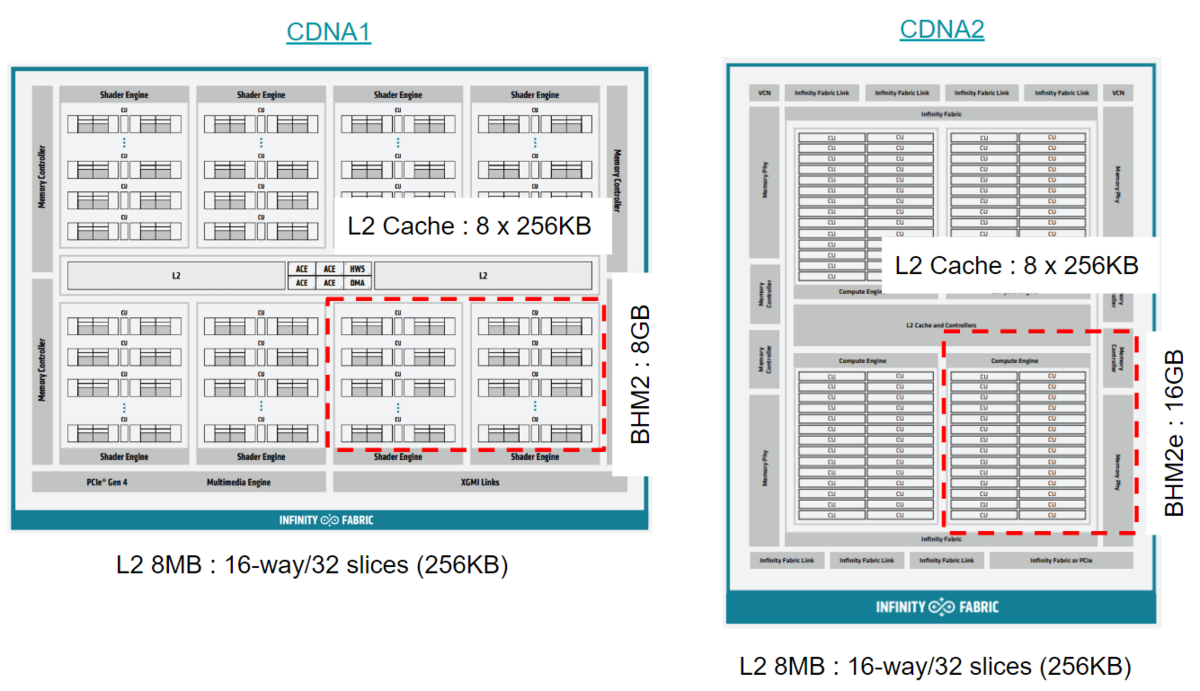

下記の2つの Whitepaper から 両方とも L2 Cache は 8MB、16-way/32slice になっていると書いてありました。

下図は説明のために図を抜粋しました。

32 slice なので、4つのメモリコントローラで分けると、1つのメモリコントローラでは 8 sliceで 2MB。256KB x 8 = 2MB。

8 slice で 8-ch になので、slice毎にチャネルが割り当てられている感じなんでしょうか?

AMD Instinct MI200" Instruction Set Architecture Reference Guide

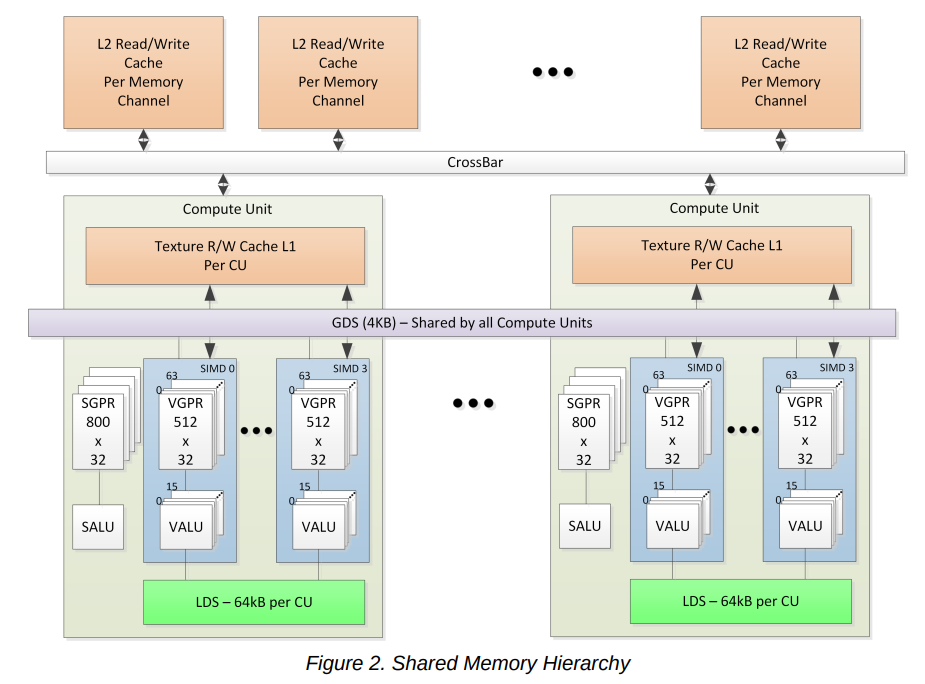

AMD Instinct MI200" Instruction Set Architecture Reference Guide に下記の図がありました。説明のために引用します。

L2 Read/Write Cache Per Memory Channel とありますので、各Memory Channel毎に L2 Cache があることが分かりますね。

"AMD Instinct MI100" Instruction Set Architecture Reference Guide にも同じような図がありました。

AMD MI250X and Toplogies Explained at HC34 に以下の図がありました。説明のために引用します。

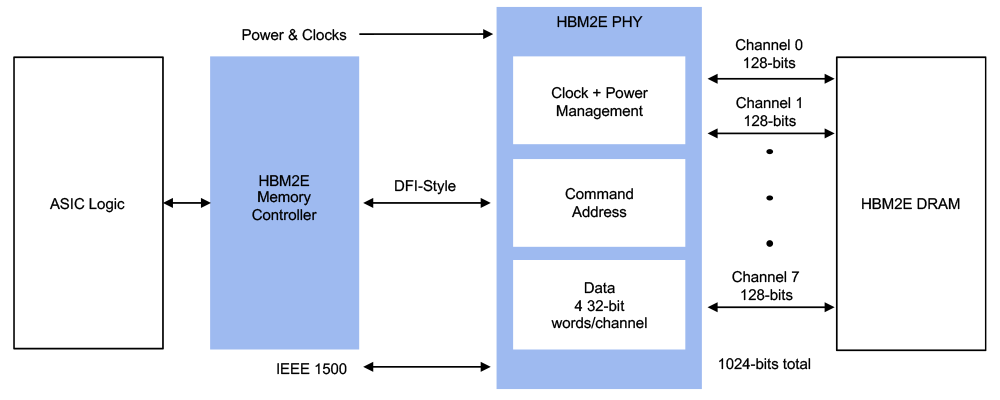

HBM2 Memory Controller

Rambus の HBM2 Memory Controller は、ここにあります。図を説明のために引用します。1チャネル128ビットで8ポートあります。

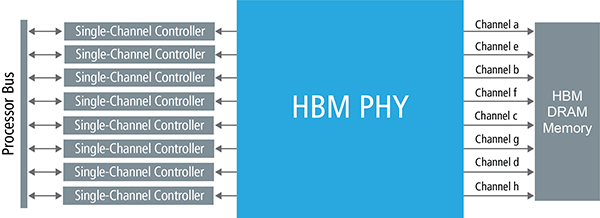

Cadence の HBM2 Memory Controller は、ここにあります。図を説明のために引用します。Channel a-hで8ポートあります。

下記の記事によると、HBM も 128bit x 8 ポートでした。

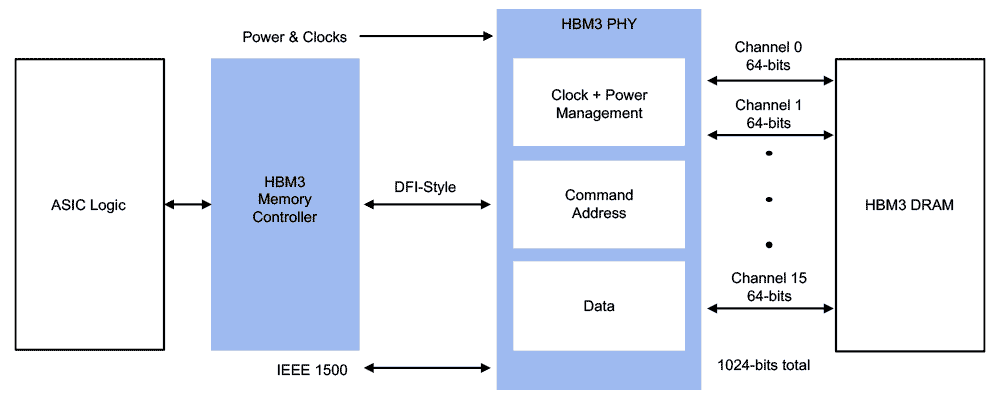

HBM3

AMD CDNA3 になると、HBM3になるんですが、HBM3ではどうなるのか?をGoogle君に聴いてみました。

図を説明のために引用します。メモリポートは 8ではなく、16になっています。

AMD CDNA3 (MI300) の GPU die を妄想してみました。AMD CDNA2 (MI210/MI250/MI250X) の 1 die の HBM2e x 4 => HBM3 x 2 にしますが、転送帯域が倍になり、ポート数を 8 => 16 にすることで構成を大きく変えることなしに実装するというものです。レイアウトできるかどうかは気になっていますが。

DDR5 と同じ?

DDR5はDDR4までと違うということをこのブログでも書きました。DDR5は転送レートが倍になったが、64ビットではなく、32ビット x 2 で使うと。

HBM2/HBM2e => HBM3 になっても、転送レートが倍になるので、ポート数を 8 から 16 の2倍にする作戦なんでしょうね。

ポート数を2倍にすると、ビット数は半分になりますが、転送レートは2倍で、ポート当たりの転送帯域は同じになりますね。

おわりに

NVIDIAのV100/A100/H100についても調べてみましたが、こちらは 512bit x 2 ポートになっています。

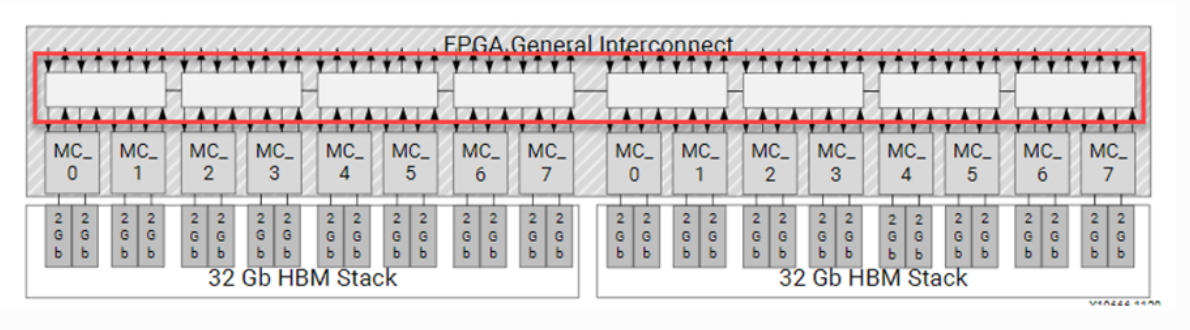

Xilinxの下記のドキュメントでは、8 ポートになっていました。

説明のために引用します。

関連記事

HBM2は8チャネルのメモリチャネルそれぞれを、さらに2つのスードチャネル(pseudo-channel)に分割する機能を備えている。128-bit I/Oラインが、64-bitずつ分割されて独立したチャネルのようにアクセスができる

「HBM2でも、基本は4個のダイで8チャネル幅だ。しかし、HBM2では、2-Hiスタックの場合は、2個のダイでも、8チャネル幅にできるようにした。HBM1では、8チャネル幅には必ず4個のダイが必要だった。ここが大きな違いで、より少ないDRAMダイ個数で、フルの帯域を得ることができるようになった」。