はじめに

テカナリエの清水さんの下記のXの投稿にあった、NVIDIAのHBM側

もちろんNVIDIA もHBM側の

— テカナリエ清水 (@techanalye1) 2023年12月20日

シリコンも開発してますよ!

メモリーメーカーに丸投げのわけないよね

(当たり前の話ですが) pic.twitter.com/3KidR12oNM

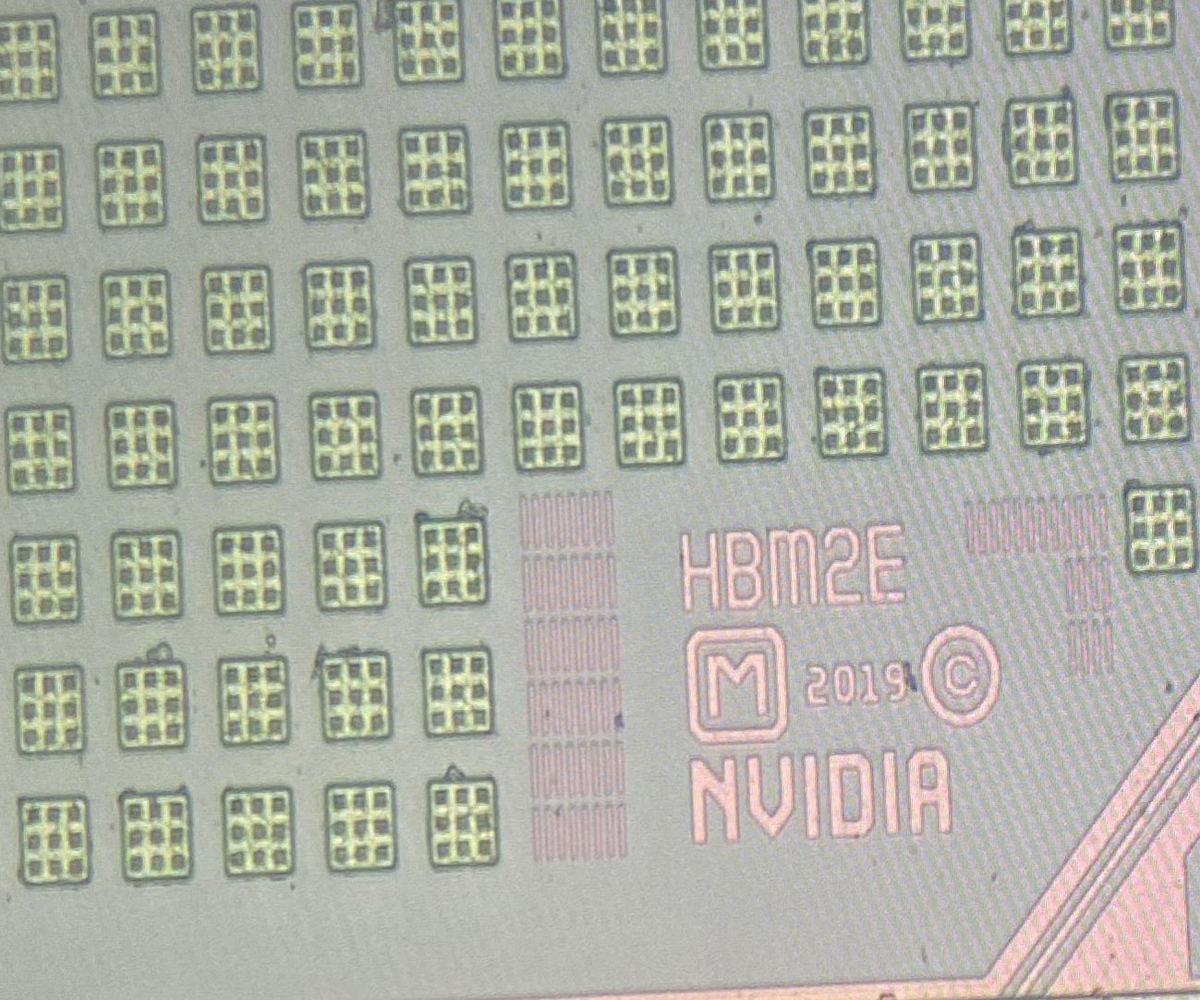

無くなるともったいないので、画像を引用します。

HBM2E、2019、NVIDIA の文字があります。

HBM2E ということなので、H100ではなく、A100 でしょうか? 2019 年だと、2020年発表のA100になり、こちらも A100 になるでしょうかね。

HBMの構成を復習

PC Watchの下記の記事にHBMの構造の図があります。

下図がその図で、説明のために引用します。

HBMは、Logic Dieの上にMemory Dieが積層されています。HBM2eでは 8 Stack、HBM3では 8 Stack/12 Stack になります。

HBM の Logic Die は、GPU と PHY にて接続しています。

NVIDIA A100のMemory Controller

NVIDIA A100 Tensor Core GPU ArchitectureのPage.19には、

The full implementation of the GA100 GPU includes the following units: ● 8 GPCs, 8 TPCs/GPC, 2 SMs/TPC, 16 SMs/GPC, 128 SMs per full GPU ● 64 FP32 CUDA Cores/SM, 8192 FP32 CUDA Cores per full GPU ● 4 Third-generation Tensor Cores/SM, 512 Third-generation Tensor Cores per full GPU ● 6 HBM2 stacks, 12 512-bit Memory Controllers

とあります。

ここで注目するのは、Memory Controller です。12個の 512-bit の Memory Controller です。

下記のブログで紹介した、AMD MI250X の HBM2e の Memory Controller は、16B/cycle (128bit/cycle) です。つまり、128-bit の Memory Controller です。HBM2e の 128bit x 8 channles = 1024bit の構成をしているので、各チャネルに対してMemory Controllerを持っていることになります。MI300Xでは、HBM3になり、8B/cycle (64bit) x 16 channel = 1024bit の構成になっています。つまり、AMDMI250X/MI300XのHBM Memory Controllerは各チャネル毎にあるということになります。

A100 (H100も)のHBM Memory Controller が AMD と同じように 128bit(HBM2e)/64bit(HBM3) ではなく、512bit なのがずーと疑問でした。

今回、テカナリエの清水さんの上記のXの投稿への写真でその理由が何となくわかりました。

GPU die 側では 512bit にして、HBMのLogic dieは各チャネルへのアクセスしているのでは?

おわりに

HBM2e だけでなく、P100/V100の時のHBM2、H100のHBM3 でも HBM側の Logic die を開発しているんでしょうかね。。。