はじめに

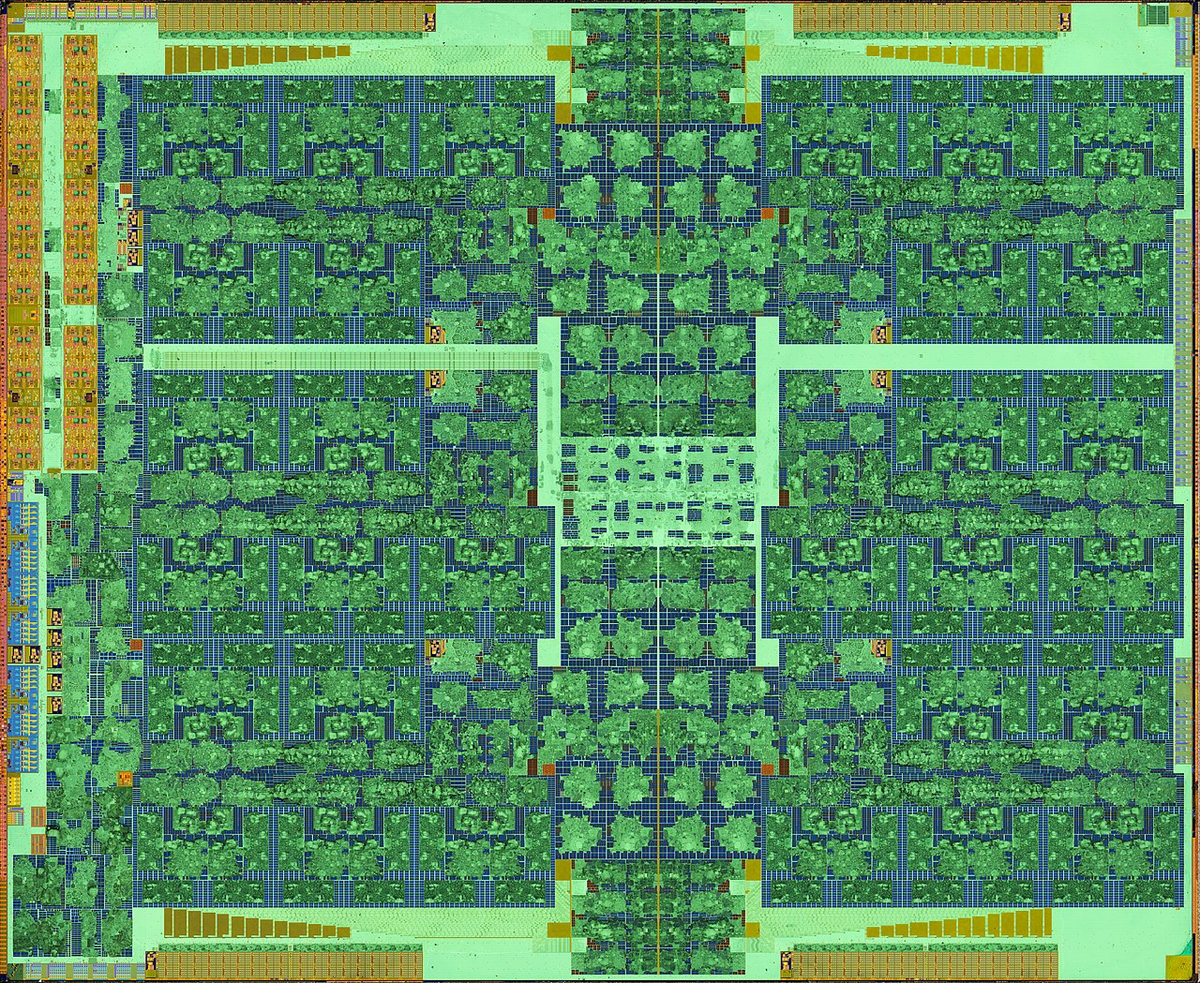

NVIDIA P100 の die shot を Wikipedia で見つけました。説明のために引用します。

かなり鮮明です。

P100 の die shot と block diagram を並べてみた

この die shot と、Whitepaper NVIDIA Tesla P100 に載っている下記の block diagram をならべてみました。

die shot に、白い部分がXBAR部分だと思っています。XBARの中で、6か所、小さな□の領域があります。これ、どうやら、GPC と XBAR との接続部分だと思います。

下図は、Whitepaper NVIDIA Tesla P100 の Page.24 のFigure 18. NVLink relationship to other major blocks in GP100 です。説明のために引用します。

下記は、die shot から GPC、L2 Cache、XBAR、High Speed Hub、Copy Engine、NVLink v1、PCIe Gen3 x16 の位置をざっくり妄想したものです。

Whitepaper NVIDIA Tesla P100 の Page.10に下記のようにありました。

memory controller is attached to 512 KB of L2 cache, and each HBM2 DRAM stack is controlled by a pair of memory controllers.

おわりに

NVIDIAのお高いGPUの中身の情報って、この P100 ぐらいしかないんですよね。P100 のアーキテクチャをベースに、V100ができて、A100 では、HBM が 4個から 6個になったので、XBARを2つに分けた感じになり、H100もそのままと。。

H100の場合は、NVLINK v4 + PCIe Gen5 x16 の他に NVLINK-C2C があるので、ちょっと変わっていますが。。。

こうやって、妄想するの好きですね。