はじめに

- BluespecのAWSteria_Infraを調べる(その1)

- BluespecのAWSteria_Infraを調べる(その2)

- BluespecのAWSteria_Infraを調べる(その3)

- BluespecのAWSteria_Infraを調べる(その4)

の続き、

今日は、HW側(Bluespec)の回路の中を調べていきます。

トップテストベンチ

トップテストベンチは、Platform_Sim/HW/Top_HW_Side.bsv です。この中で、ここで、AWSteria_HW をインスタンスしています。

// The top-level of the AWSteria design AWSteria_HW_IFC #(AXI4_Slave_IFC #(16, 64, 512, 0), AXI4_Lite_Slave_IFC #(32, 32, 0), AXI4_Master_IFC #(16, 64, 512, 0)) awsteria_hw<- mkAWSteria_HW (clkdiv1.slowClock, clkdiv2.slowClock, clkdiv3.slowClock, clkdiv4.slowClock, clkdiv5.slowClock);

AWSteria_HW

AWSteria_HW は、ここにあります。構造は下記のようになっているようです。

// ================================================================ // This package contains a sample AWSteria_Infra app, // i.e., a mkAWSteria_HW module with AWSteria_HW_IFC interface. // This specific application contains // - a 2xN AXI4 fabric, where N = 1,2,3,4 (64b addrs, 512b data): // - an AXI4-Lite-to-AXI4 adapter // The schematic is: // // +==AWSteria_HW================================================+ // | +=AXI4-Fabric=+ | // AXI4_S----------------------------------------+ +-AXI4_M to DDR A // | | | | // | | +-AXI4_M to DDR B // | | 2xN | | // | | +-AXI4_M to DDR C // | | | | // | +-AXI4_S +-AXI4_M to DDR D // | | +=============+ | // | +=Adapter=+ | | // AXI4L_S-----------------AXI4L_S AXI4_M-+ | // | +=========+ | // | | // +=============================================================+

上記の図から外部とは、

- AXI4_S

- AXI4L_S

の2つのスレーブインターフェースがあります。

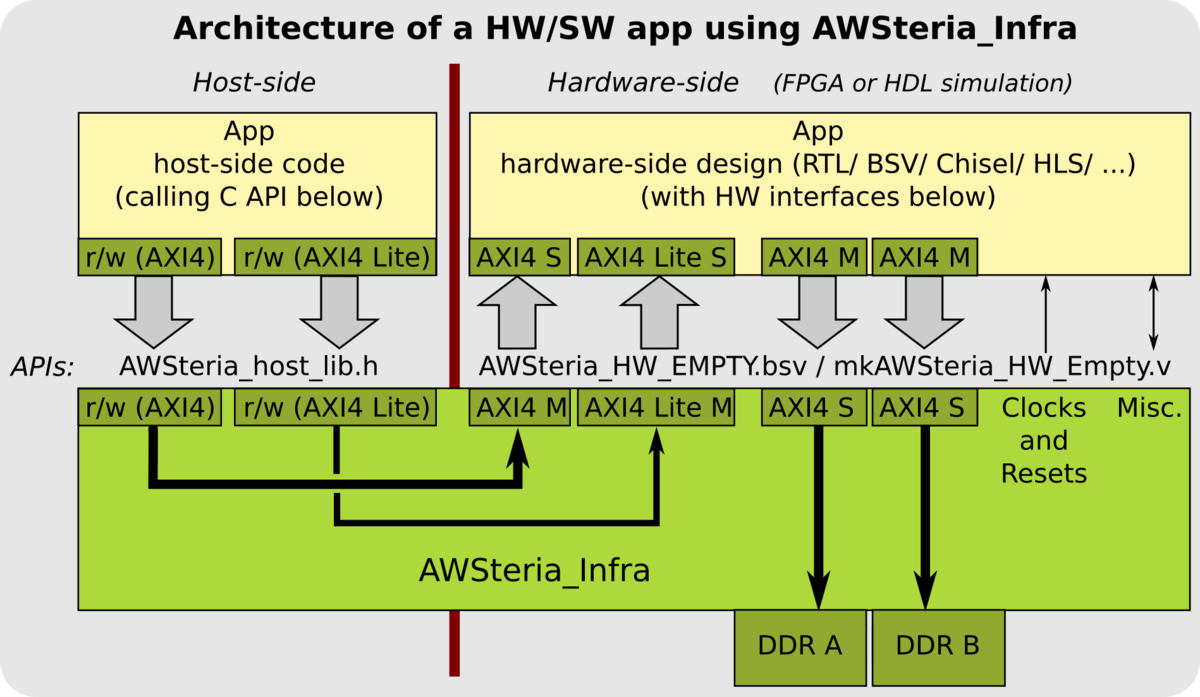

下図は、全体の図です。右上のAppのところが上記の回路に相当します。図とちょっと違うのは、DDRへのポートが4ポートになっていることですかね。

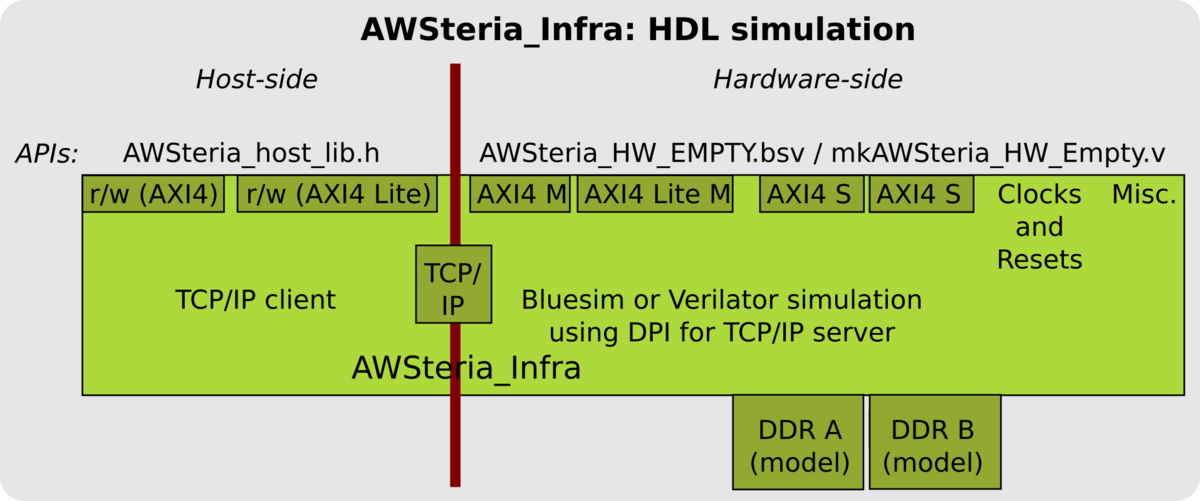

HDL Simulationでは、AWSteria_Infraの部分が下記のような構成になっています。

おわりに

AWSteria_Infra の回路部分はSlaveデバイスで、DDR Memoryが4ポート接続されている感じになっています。