はじめに

Google TPU v5e が chiplet だったというのは下記のブログで紹介しました。

TPU v5e は、Compute die + I/O die なので、TPU v5p も Compute die + I/O die のはずと思い、調べまくったら、見つかりました。

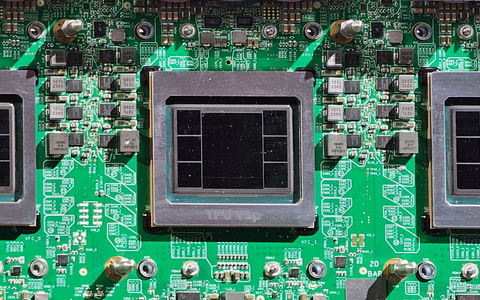

TPU v5p の 写真

下記の PC Watch の記事の中に、Google TPU v5p のパッケージの正面からの写真がありました。

下記がその写真です。説明のために引用します。

まず、HBMが両サイドの3個づつありますが、どうもバランスが悪いです。

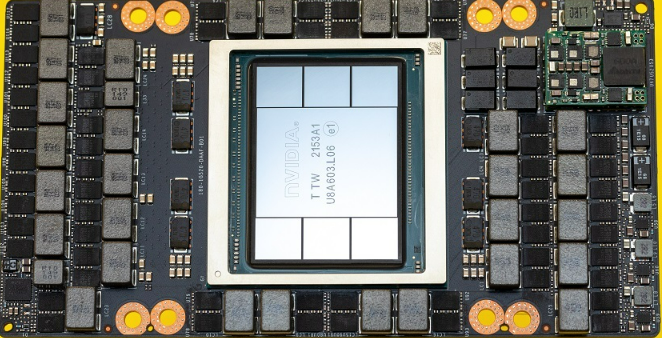

下記の図は、NVIDIA H100 です。[こ](https://japan.cnet.com/article/35187234/)こから説明のために引用します。HBMがキレイに並んでいます。

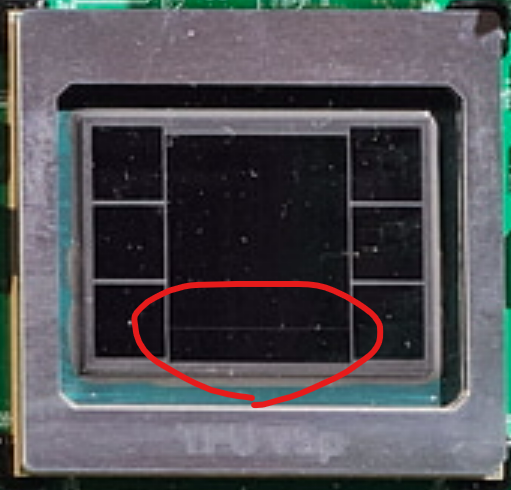

もう一度、TPU v5p の写真を見てみましょう。拡大して、引用します。下側に横線があります。この部分で die が分かれています。

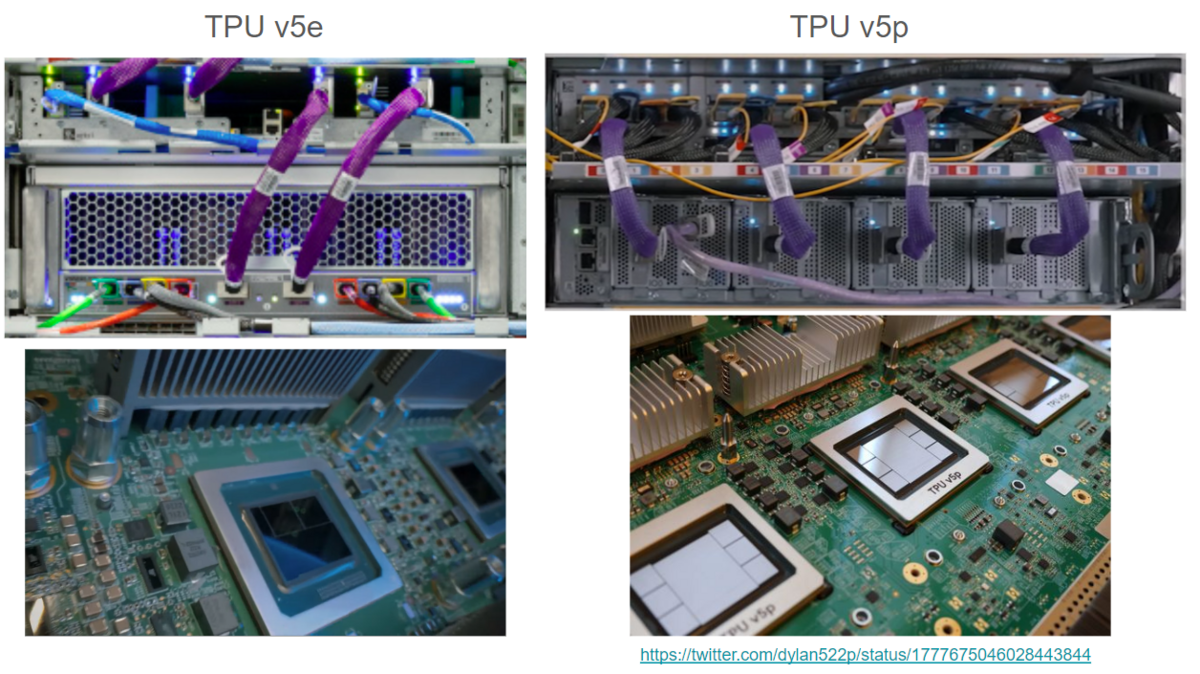

v5e と v5p を比べてみる

下図の右下の図は、ここからの引用です。それ以外は、Googleの公式Youtubeから引用しています。

ボードの手前側にコネクタがあると思います。

v5e は、左側に I/O die が、v5p は手前側に I/O die があります。

- v5e : (PCIe Gen5 x8 (たぶん) + 400Gbps x 2) が 4組

- v5p : (PCIe Gen5 x16 + 800Gbps x4) が4組

おわりに

TPU v5e / v5p は、chiplet になっていることが確認できました。

となると、v6e / v6p も chiplet になるのでしょうか?