はじめに

NVIDIA Grace の 内部ブロック図は、NVIDIA Grace CPU Superchip Whitepaperにある下記の図(説明のために引用します)が一般的です。

もう少し具体的なものはないかな?と思ってい調べて出てきたので記録に残します。

違う資料

下記の図は、この資料の15頁にあるものです。説明のために引用します。NVIDIA Grace CPU Superchip Whitepaperのブロック図とは多少違います。

2つのブロック図を並べてみました。合っていそうです。違いは左側の上下に2個づつ空いているところは右側では何かがあります。

Grace の Die shot

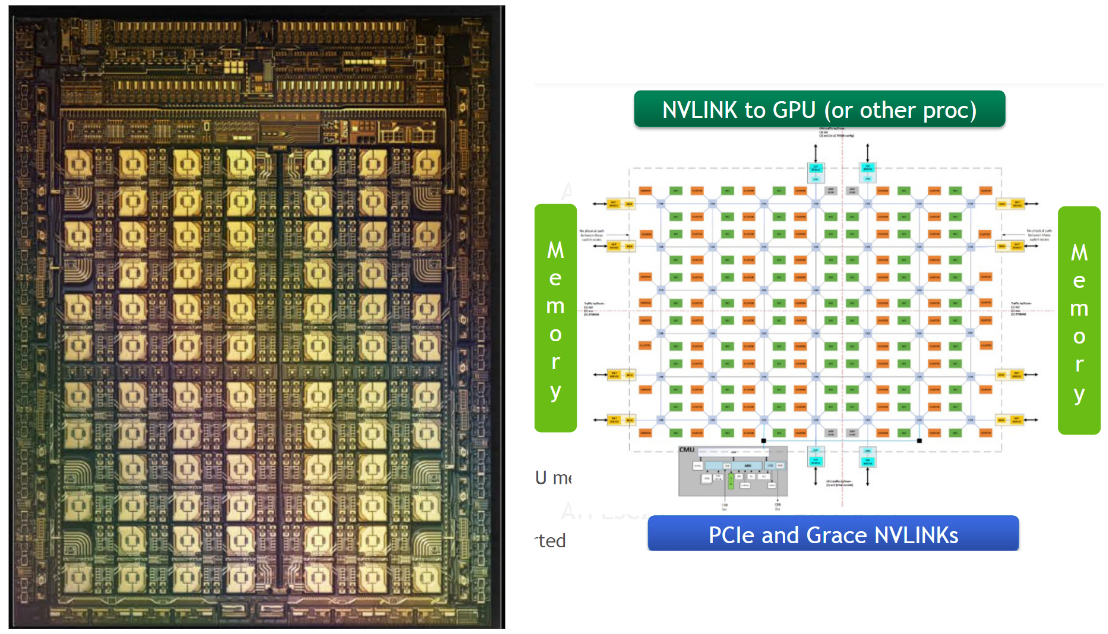

下記のXの投稿からGrace の die shotを説明のために引用します。

Hmmm… how many cores does this mean? pic.twitter.com/W5D3PmOd48

— Longhorn (@never_released) 2021年11月13日

上記のブロック図と比較のために並べてみました。非常に分かりやすくなりました。

左の図では、下が x12 clNVLINK/PCIe + x56 PCIe Gen5 (4 x PCIe Gen5 x16)、上が NVLink C2C

しかしながら、2022年9月21日のブログに書いた時は、

上が x12 clNVLINK/PCIe + x56 PCIe Gen5 (4 x PCIe Gen5 x16)、下が NVLink C2C

どちらが合っているのでしょうかね。

NVIDIA Grace CPU Superchip Whitepaperの図を見直してみると、下が NVLINK C2C になっていますね。

帯域

x4 x PCIe Gen5 x16 は、x4 x 64GB(片側)。NVLink C2C は、片側450GB/s。

昨日の内部バスの周波数の記事では、76GB/s としていたので、x4 x PCIe Gen5 x16 それぞれに 1つ割り当てればOKっぽい

NVLink C2C の場合は、どうなる?

下図は下側のNVLink C2Cの部分の拡大図、説明のために引用します。左右に4個づつ塊があるように見えます。となると、450GB/s を 8個で割って、56.25GB/s。 でも、交点は7個。。。あれ、

おわりに

内部バス(Fabric) と NVLINK C2C の接続がまだはっきりしません。。。

うーん、どうなっているのだろうか?