はじめに

Hotchips 33 にて、Graphcoreが講演しました。

タイトルは、"Graphcore Collossue Mk2 IPU" 。Mk2 IPU なので既にいろいろと発表しているので、追加で何か?あるのかな。。。と

講演ビデオは、Youtube で公開されています。

気になったのは、”Why No HBM?"

スライドの最初の方は既に発表があった内容ベースだったのですが、後半の "Why No HBM" からの4スライド。説明のために引用します。

- Momory capacity determines what an AI can do: bandwidth just limits how fast.

- GPU and TPU try to solve for bandwidth and capacity simullltaneously, using HBM.

- HBM is very expensive, capacity-limited, and adds 100W+ to the processor thermal envelope.

- IPU solves for bandwidth with SRAM, and for capacity with DDR

実行できるモデルは、メモリ容量であり、帯域は速くできるかどうかだけ。GraphcoreのIPUは、容量はDDRを使い、帯域は内部のSRAMで解決したと。

そう、GraphcoreのIPUは、内部のSRAMだけでチップにはDRAMは接続していない。しかしながら、M2000内のGateway-SoCにはDDR4が最大512GB(内、448GBを使用)が付いています。このDDR4を使って、大きなモデルにも対応しています。M2000には4つのIPUがあり、パイプライン動作にて大きなモデルを実行しています。とはいえ、448GBでは現在の大きなモデルをサポートできないと思います、IPU-Pod16なら4台のM2000なのでざっくり1.8TB、IPU-Pod64なら7.2TBのDDR4メモリがあるのでそれなりの大きさのモデルまで実行できそうです。

各チップに対して112GBのDRAMがいると考えると、NVIDIA A100 80GBバージョンより多いとも言えますね。

とはいえ、昨日のブログの Cerebras Systems の MemoryX の 4TB - 2.4PB の Memory & Flash Storage には及びません。

DRAMのコスト

下記のスライド(説明のために引用します)は、DRAMの経済性ということで、HBM2 (20nm) に比べて、DDR4 (18nm) は Systemの 1GB単位のコストが 10倍違うということに。

Placing Model State

次のスライド(説明のために引用します)は、Model state をどこに置くのか?というものです。どんなモデルでも Optimizer state は、DRAM 上にありますが、Model state はモデルのサイズによProcessor または DRAM のどちらに置くかが決まります。外部DDの帯域が下記の2つのケースに置いて、十分であると。。。

Off-chip DDR bandwidth suffices for:

- Distributed optimizer states at all scales

- Streaming weight states for large models

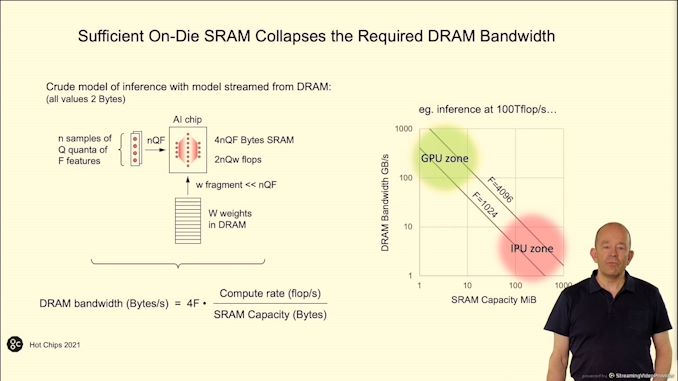

では、どうでそうなるのでしょうか?というのが次のスライド(説明のために引用します)。十分なSRAMの容量があれば、HBMではなく、DDRでもOK。とということなんでしょうか? (とはいっても。eg. inference at 100T flop/s とあるのが気になりますが)

TSMC 3nm でチップを作るとか?

MK1 (16mn) のSRAM 300MB を MK2 (7nm)では、3倍の900MBにしたんだけど、3nm だとどうなるのだろうか? 7nm に対して、2倍ぐらい入るのかしら?

3nm で実装するとなると、SRAMの容量も倍ぐらいの2GBぐらいにはなりそうですね。2GBのSRAMがあるということは、外部のDDRの容量も増やして、より大きなモデルにも対応できるようになる。そうなると、M2000のGateway-SoCの512GBのDDR4じゃ、足りなくなり、もっと多くのメモリを接続できる必要になるんだと思います。

この部分を自社で開発するのかなー、と思いましたが、GraphcoreのCareersを見ると、そんな職は募集していないです。となると、どこかのSoCを使うのかな。。。。2TBとか接続できるSoCならいろいろとありそうだし。。。(4つのIPUをPCIe GenXで接続しているので、PCIe Controller が最低4個、100GbEのMellanox のCardや SSDとの接続もあるので、PCIe Controoler ももう少し多く必要になると思います。ちなみに、M2000 の Gateway-SoC は、XilinxのZynq UltraScale+ MPSoCの VUP9 で PCIe Controller が6個載っています。