はじめに

NVIDIAがGPUのKernel Modulesを公開したので、ソースコード解析をしてみる、(その3)

NVIDIAの falcon micro processor

Wikipedia )によると、

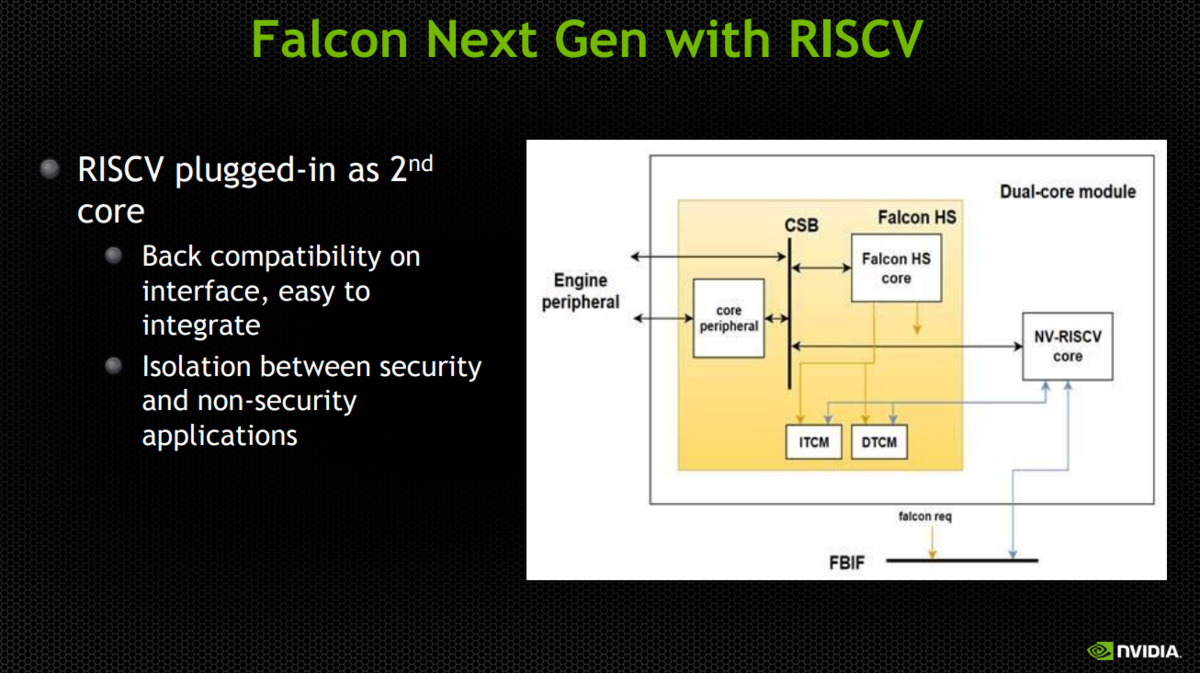

Around the year 2006 Nvidia introduced FALCON (FAst Logic CONtroller) to their GPUs. At the 4th RISC-V Workshop in July 2016 Nvidia employees introduced their plans to replace FALCON with a new proprietary custom design based on the RISC-V instruction set.[18]

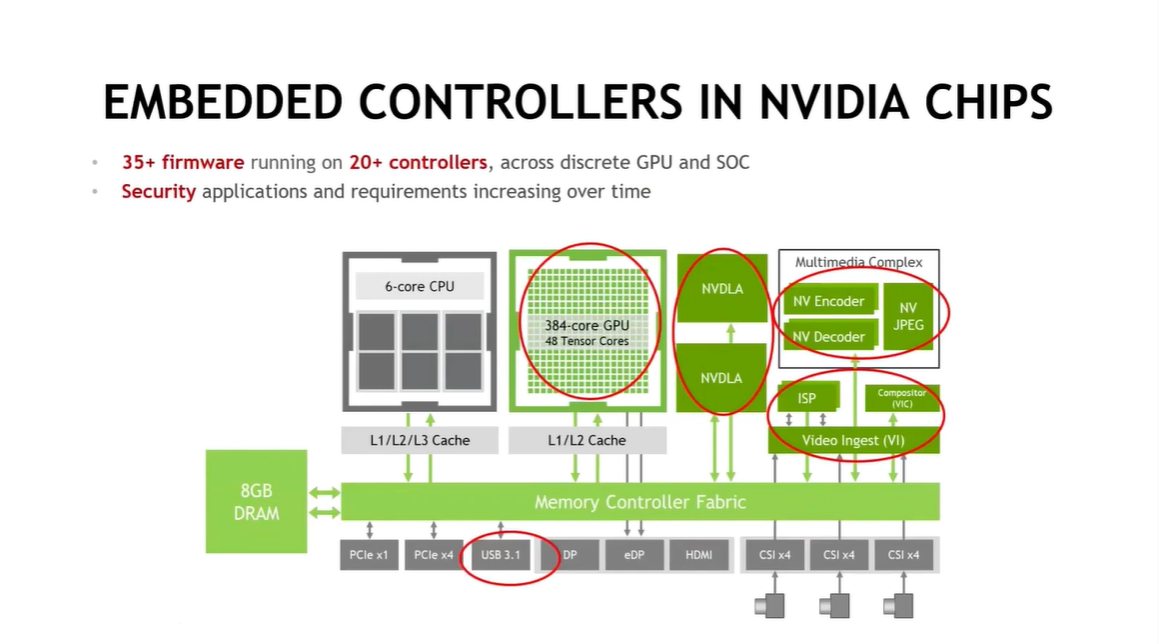

下記のビデオ : Keynote: NVIDIA’s secure RISC-V processor - Frans Sijstermans & Joe Xie, NVIDIA、によると、35+ firmware running on 20+ controllers across discrete GPU and SOC ということでした。

- RISC-Vベースのソリューション(Peregrine)

今回は、RISC-V/Falcon に、ついて、

RISC-V/Falcon

NVIDIAのGPU内部にFalconというCPUがありましたが、下記の講演にて、そのCPUをRISC-Vにするということを発表します。

ソースコードは、ここ

- ampere は、ga100 と ga102

- turing は、tu102

どうやら、ampere/turing からっぽいですね。

ga102 の RISC-V/Falconに関するレジスタのヘッダーファイルは、ここ

- RISCV_IRQMASK

- RISCV_IRQDEST

- RISCV_CPUCTL

- RISCV_BCR_CTRL

ga100 の RISC-V/Falconに関するレジスタのヘッダーファイルは、ここ

- RISCV_CORE_SWITCH_RISCV_STATUS

- RISCV_IRQMASK

- RISCV_IRQDEST

tu102 の RISC-V/Falconに関するレジスタのヘッダーファイルは、ここ

- RISCV_CORE_SWITCH_RISCV_STATUS

- RISCV_IRQMASK

- RISCV_IRQDEST

Falcon ID

ここ にあった、Falcon ID。なんか、いっぱいある。ということは各機能モジュールにはFalconが付いているのかな?

#define LSF_FALCON_ID_PMU (0U) #define LSF_FALCON_ID_DPU (1U) #define LSF_FALCON_ID_GSPLITE LSF_FALCON_ID_DPU #define LSF_FALCON_ID_FECS (2U) #define LSF_FALCON_ID_GPCCS (3U) #define LSF_FALCON_ID_NVDEC (4U) #define LSF_FALCON_ID_NVENC (5U) #define LSF_FALCON_ID_NVENC0 (5U) #define LSF_FALCON_ID_NVENC1 (6U) #define LSF_FALCON_ID_SEC2 (7U) #define LSF_FALCON_ID_NVENC2 (8U) #define LSF_FALCON_ID_MINION (9U) #define LSF_FALCON_ID_FBFALCON (10U) #define LSF_FALCON_ID_XUSB (11U) #define LSF_FALCON_ID_GSP_RISCV (12U) #define LSF_FALCON_ID_PMU_RISCV (13U) #define LSF_FALCON_ID_SOE (14U) #define LSF_FALCON_ID_NVDEC1 (15U) #define LSF_FALCON_ID_OFA (16U) #define LSF_FALCON_ID_SEC2_RISCV (17U) #define LSF_FALCON_ID_NVDEC_RISCV (18U) #define LSF_FALCON_ID_NVDEC_RISCV_EB (19U) #define LSF_FALCON_ID_NVJPG (20U) #define LSF_FALCON_ID_END (21U)

NVIDIA Falcon Security によると、

On all Falcons other than PMU (the "kitchen sink" Falcon) and DPU (the Falcon that services display),

とあります。ね。

- PMU (the "kitchen sink" Falcon)

DPU (the Falcon that services display)

MINION は、NVLINK 関連っぽい

- SOE は、NVSWITCH 関連っぽい

FALCON の中で、RISC-V を抱えているのは

- GSP

- PMU

- SEC2

- NVDEC

だけなんですかね。

Boot Device もいろいろ?

/*! * Bootstrap Owner Defines */ #define LSF_BOOTSTRAP_OWNER_PMU (LSF_FALCON_ID_PMU) #define LSF_BOOTSTRAP_OWNER_SEC2 (LSF_FALCON_ID_SEC2) #define LSF_BOOTSTRAP_OWNER_GSPLITE (LSF_FALCON_ID_GSPLITE) #define LSF_BOOTSTRAP_OWNER_DEFAULT LSF_BOOTSTRAP_OWNER_PMU

おわりに

今回は、RISC-V/Falcon の部分について、見てみました。

P.S

linux の tegra にはいっている NVDecのコードでも falcon が使われています。

Tegraの USB (XUSB) にも Falcon がありますね。