@Vengineerの戯言 : Twitter SystemVerilogの世界へようこそ、すべては、SystemC v0.9公開から始まった

はじめに、

なんとなく、NVIDIAの GTC21 の GRACE のビデオを観た。基調講演の時に観たと思ったのだが、見直してみると得るものがあってよかった。 今日のブログでは、そのことを記録のために、書いておきます。

見直したビデオ

見直したビデオは、こちら。

NVIDIA GTC 2021 Keynote Part 6: Amazing Grace - an ARM CPU for Giant-Scale AI and HPC

Armコア搭載のGRACEについて。

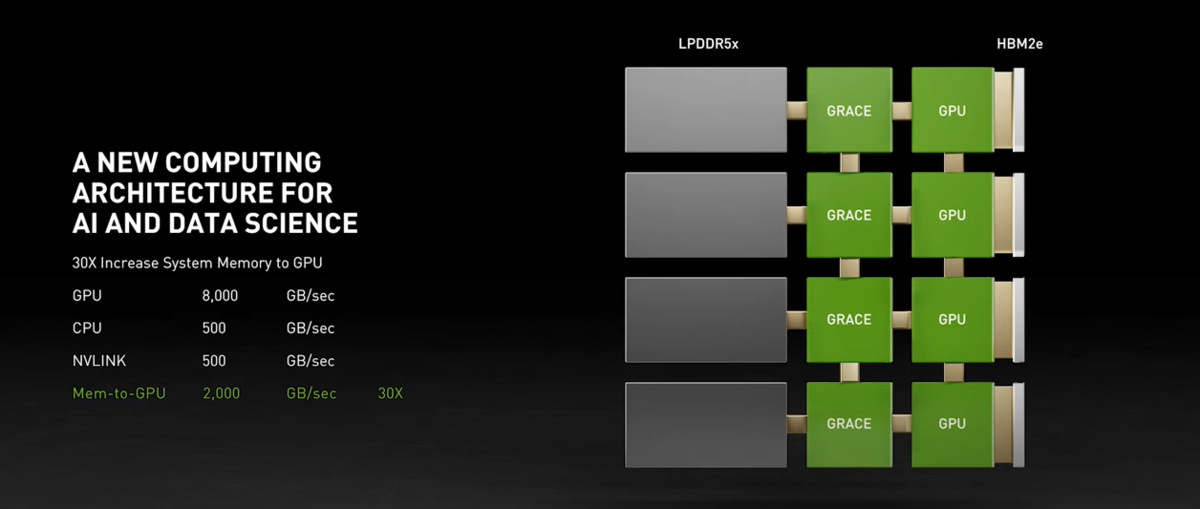

GPU <=> CPUに付いているメモリ帯域の向上

従来:4基のGPUをx86-64のCPUチップに PCIe Gen4 x16 でそれぞれ接続している場合。

- GPUに付いているメモリの帯域は、8000 GB/s (HBM2になったので帯域はめっちゃ大きい)

- CPUに付いているメモリの帯域は、200 GB/s 。

- CPUとGPU間の接続が PCIe Gen4 x16 で 16GB/s 。4個のGPUだと、64GB/s。ここがボトルネック。

下図は、2:14のところのスナップショットです。説明のために引用します。

これに対して、GRACEを使うと、

- CPUに付いているメモリの帯域は、500 GB/s。

- GPU、1つに対して、1つのGRACEを第4世代NVLinkにて接続する。第4世代NVLink は500 GB/s 。

- CPUに付いているメモリの帯域と第4世代NVLinkの帯域は同じ 500 GB/s 。4基で2000 GB/s

x86-64 に対して、GRACE は、CPUに付いているメモリへの帯域が 64GB/s => 2000 GB/s となり、約30倍。。。

下図は、2:42のところのスナップショットです。説明のために引用します。

DGX と同じぐらいの筐体

下図は、4:19のところのスナップショットです。説明のために引用します。

4枚のボードの下には、それぞれ、2個のコネクタ接続部らしいものが見えます。 また、ベースとなっている基板には3つの大きなヒートシンクが載っています。これは3個のNVLink Switch用のヒートシンクだと思います。DGX A100では6個のNVLink Switchを搭載していますが、GPUが8個から4個に減ったので、NVLink Switchも半分の3個に。

帯域の時に、4つのGRACEについて説明したので、DGXのものも4個のボードになっているのだと思います。

下図は、4:23のところのスナップショットです。説明のために引用します。

A100の左にあるのが GRACE のようです。A100より大きいです。DGX A100 には A100 のモジュールが8個入っていますが、下図のサイズの基板だと8枚は無理なので、4枚にしたのでしょうか?

スライドにはないのですが、x86-64ベースの DGX A100 に対して、GRACE x8 + A100 x8 は、10倍速いようです。 となると、GRACE x4 + A100 x4 の構成で 5倍速いということになりますね。

下図は、5:38のところのスナップショットです。説明のために引用します。

図にあるように、Ampere Next が 2022年。Grace が 2023年になっています。

ということは、上記の基板は GRACE ではないが Armコアベースで A100 に接続するために、第3世代NVLinkで接続しているということになっているんでしょうね。 上の図にそのチップを赤丸で入れてみました。見事にキレイな図になりました。今回の発表のArmコアのチップもコードネームがあって A100 + BlueField2 との組み合わせで作ったのだと思います。

今回のビデオにあった DGX っぽいもの。それが、GraceベースのDGXのプロトタイプだったんですね。A100では、12本の第3世代NVLink で 600 GB/s 。2本を使って GPU間の接続をするので、100 GB/s 。GRACEとAmpere Nextの組み合わせだと、Ampere Nextは、2個のGPUと1個のGRACEと接続する。また、Ampere NextはA100と同じように12本のNVLinkが必要と考えると、12 - 2*2 = 8 本をGRACEの接続に使える。8本で500 GB/s ということは、2本で 125 GB/s 。。100 GB/s => 125 GB/s なら実現な線ですね。

今回のGRACEのプロトタイプも第3世代NVLink を 4組持っていて、A100と接続しているということになりますね。基板の裏面のコネクタは他の基板のGPUに接続するための第3世代NVLink が2組出ていることになりそうですね。コネクタが大きいのは信号線だけでなく、電源・グランドをたくさん取るためだと思います。

GRACE はどんな感じ

再度、下図を見てみます。BlueField-2は8コア、BlueField-3は16コアになっているのが分かります。BlueField-4はなんと32コアになっていますね。 そんな感じで、Graceを見てみると、7 x 12 = 84コアっぽいんですよ。。 こんなにいっぱいのコア搭載しているのって、AmpereのAltra(GPUの名前ではなく、Ampereという会社)のチップぐらいですかね。この Altraは80コア、72bit DDR4-3200 が 8チャネル、128 laneのPCIe Gen4。DDR4-3200で、25.6GB/sなので、200 GB/s程度ですね。これは、上記の x86-64のCPUのメモリ帯域と同じですね。

GRACEのプロトタイプではLPDDR5で 400 GB/s を実現しているのかな? SamsungのLPDDR5のサイトでは、6,400Mbps, 51.2 GB/sとあります。ビデオでは 8個のDRAMしか載っていないので、51.2 GB/s * 8 = 414.4 GB/s になり、第3世代NVLink x 8 = 400 GB/s を超えますね。

おわりに

GTC21の 基調講演の GRACE関連のビデオを見直して、今回のビデオにあったボードはGRACEのプロトタイプであり、ここからが起点で

- CPU : GRACE ベース (ARMメニ―コア)

- GPU : Ampere ベース

- DPU : BlueField ベース

による DGX ができ上げったということですね。

- 2021 : プロトタイプ

- 2023 : 第1世代 GRACE

- 2025 : 第2世代 GRACE

って感じです。

あ、再度、下図。。。どこかで見たな。。。

Intelの tick - tock だ。。。

IntelはCPUだけだけど、NVIDIAは、GPUとCPUでやろうとしている。。