はじめに

2021年8月19日(米国時間)に行われた、Intel Architecture Day 2021 にて、次世代データセンター向けプロセッサとなる「Sapphire Rapids」の詳細を発表しました。

既にいろいろな情報がリークされていましたが、Intelからの正式な詳細な発表は今回が初めてです。

Cloud Watchの記事

下記のCloud Watchの記事によると、次世代のXeon SP となる Sapphire Rapids は 2022年の初頭に投入される計画となっていると、 cloud.watch.impress.co.jp

ざっくり知りたいのならこの記事を読めばいいのではと。

ビデオ

Sapphire Rapids - Architecture Day 2021 | Intel Technology が発表時のビデオで、20分の内容です。

Die は?

下記の記事の最初に、パッケージ上に実装されている4つのdieの写真が載っています。

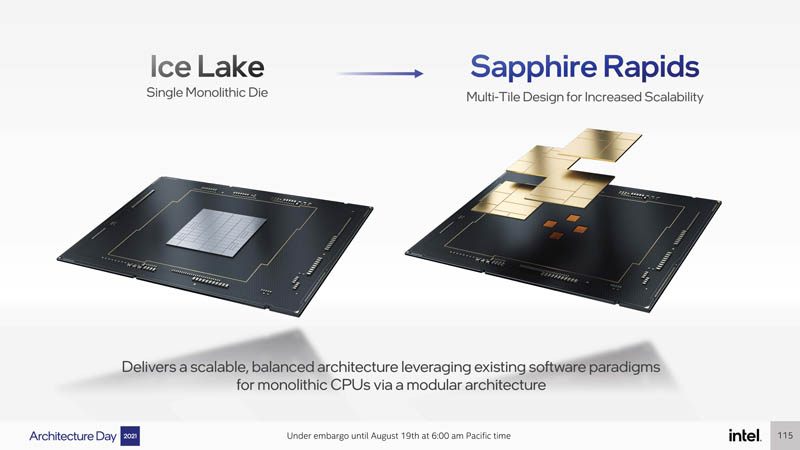

下図は、Ice Lake と Sapphire Rapids の違いを示すスライドです。説明のために引用します。Ice Lakeでは、1つの die のみですが、Sapphore Rapids では 4つのdie を EMIB (オレンジの小さな四角い半導体)を使って接続しています。4つの die は、同じ die ではなく、2種類の die (ミラーになっている) から構成されています。

リークされていた情報では、Sapphire Rapids には、Altera 10M16Y180Gが載っている。。。これ、MAX10かな。。

元ツイッターは、これかな。。。

最初に紹介した記事の写真を再度見てみましょう!

MAX10 があったところには、ボールが載るようにはなっていますが、チップは載っていませんね。

die には、何コア載っているの?

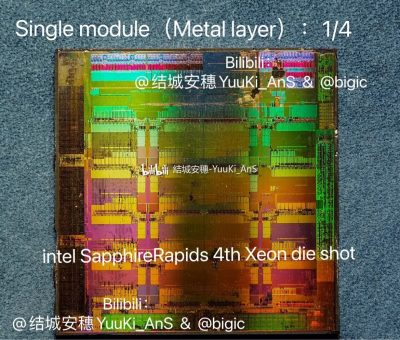

下記の記事に、Sapphire Rapids のシリコン写真が載っています。

Sapphire Rapids die shot shows 60 cores, but only 56 will be active on top SKU

説明のために、写真を引用します。仕様としては、56コアが最大コア数になっていますが、下記の die を見ると、15コア載っているように見えます。右側の上から2番目のところがコアではない。

この写真の左側に3つのブロック、下側に2つのブロックがあります。この部分は 他の die を接続するための EMIB なんですかね。 写真の上側は、PCIe Gen5 x16 と UPI 2.0 が出ていますが、それ以外にも HBM2x への EMIB もあるっぽいです。

下記の記事にも、die の写真が何点か載っています。その内、1枚を説明のために引用します。

上の2個の die 。縦に3組、横に2組の EMIB で接続しているのが分かります。

おわりに

AMDがEPYCにて、4 die を 1つのパッケージに入れて市場に導入したのが、[June, 2017のNaple](https://en.wikichip.org/wiki/amd/epyc)s。 第2世代では、I/Oチップを分離し、CPU die x4 + I/O die の構成に:August, 2019のRome、March, 2021のMilan。

そして、2022年のGeoa では、CPU die x 6 + I/O die の構成にして、1パッケージで 96コア、2 Sockets システムで 192 コアのシステムになります。

Intel Sapphire Rapids が (14コア x4) x 2 = 112 コア vs AMD EPYC Geoa が (8コア x 12 die) x 2 = 192 コア。コア数はまだ AMD の方がまだまだ多いです。