はじめに

このツイートで知った、AMDのEPYCに関する講演ビデオを観ました

AMD talks about being pad limited on CPU designs. This explains future use of advanced packaging

— Dylan Patel (@dylan522p) 2022年1月8日

"One example is the memory interfaces. They are not limited by the logic area, they are limited by the size of the bumps to drive the external connections."https://t.co/zzCJ9bs6W5

The Motivation for Chiplets and their Adoption in AMD Processors

AMD EPYC

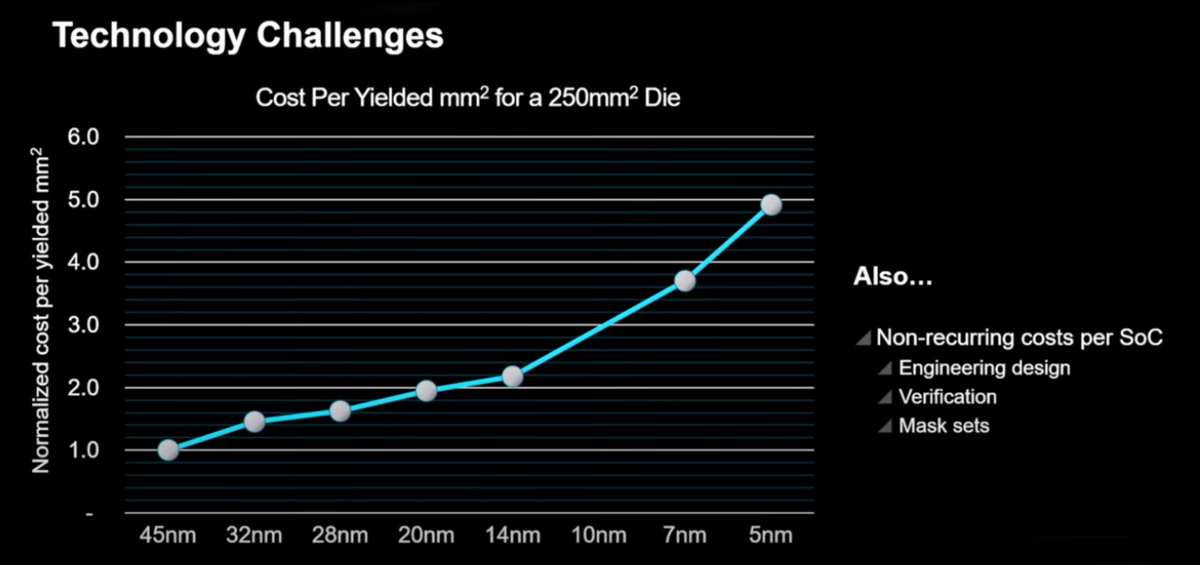

5分ぐらいのところの下記のスライドを説明のために引用します。

14nm => 7nm になると、同じイールドでコストが約2倍になると。

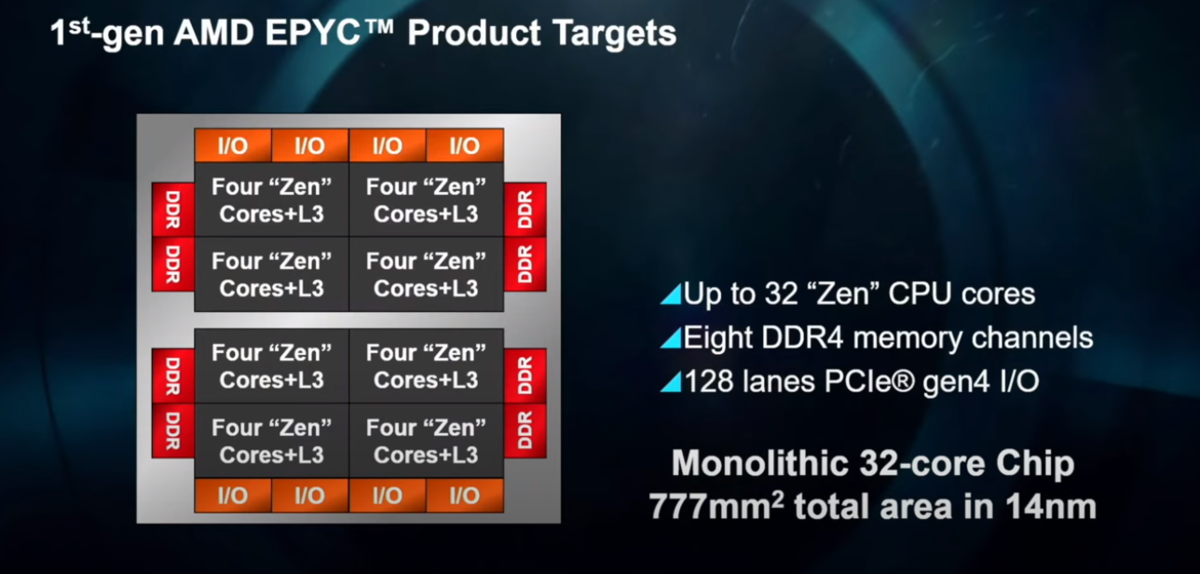

15分ぐらいのところの下記のスライドを説明のために引用します。

1st gen AMD EPYC の 32コアを 1die で実装した時のサイズは、14nm で 777mm2

16:30ぐらいのところの下記のスライドを説明のために引用します。

- 213 mm2 per chiplet (14nm)

4x => 852mm2 total <= 777 mm2

+10 % silicon area

- 0.59X cost

25:30ぐらいのところの下記のスライドを説明のために引用します。

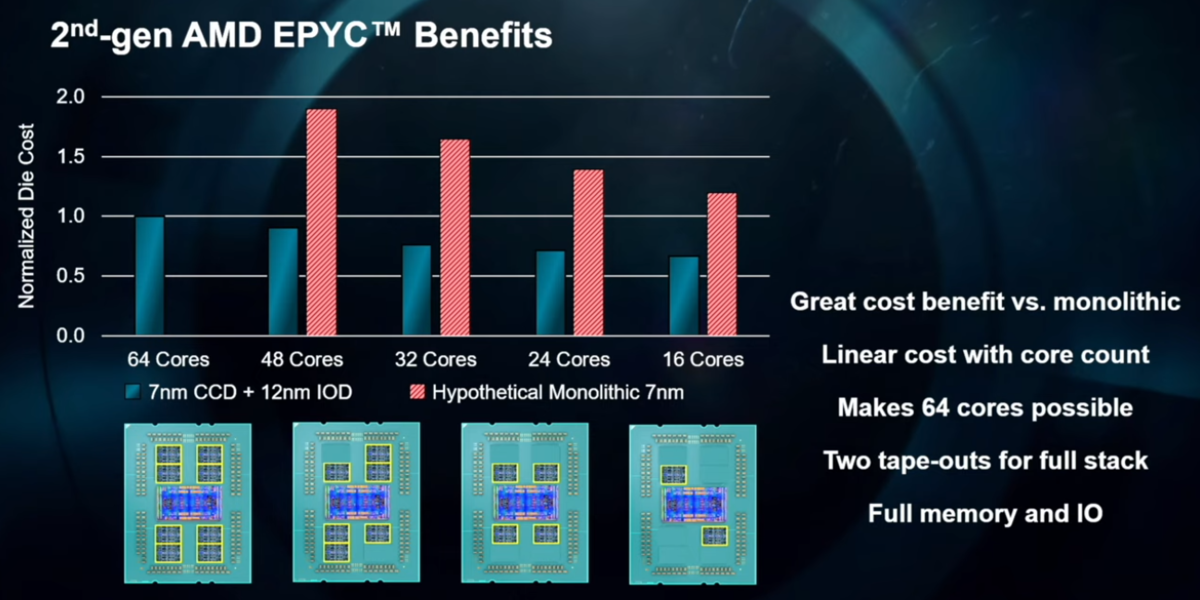

44:00ぐらいのところの下記のスライドを説明のために引用します。

16 Cores / 24 Cores / 32 Cores / 48 Cores / 64 Cores、それぞれに対しても、1 die で開発する時よりもお安くなったようです。

[46:30ぐらいのところ](https://youtu.be/97gPMIbYSNI?t=2790]の下記のスライドを説明のために引用します。

EPYC ROME と Ryzen ( 2 x CCD ) のレイアウトおよび配線の図

おわりに

この講演ビデオ、AMDの chiplet および package に関する情報満載です。