はじめに

Xilinx AI Engine の シミュレータ (aiesimulator) を動かしてみた(その5)です。

今回は、

- --dump-vcd オプション を指定して、波形ファイルをダンプしてみます

- --profile オプションを指定して、プロファイルを取ってみます

- --onlinw オプションを指定して、

波形ファイルのダンプ

aiesimulator --pkg-dir=Work --input-dir=data --output-dir=data --dump-vcd=vadd

--dump_vcd オプションには、.vcd という拡張子は必要ありません。

vadd.vcd

が生成されました。

また、data/aiesim_options.txt の中に AIE_DUMP_VCD=vadd が設定されました。

cat data/aiesim_options.txt AIE_PKG_DIR=/mnt/c/Users/haray/home/src/aie_hw/Work AIE_DUMP_VCD=vadd

プロファイルを取る

aiesimulator --pkg-dir=Work --input-dir=data --output-dir=data --profile

data ディレクトリの下に4つのプロファイルデータが出力されました。

ls data/profile* data/profile_funct_24_0.txt data/profile_funct_24_0.xml data/profile_instr_24_0.txt data/profile_instr_24_0.xml

- data/profile_funct_24_0.txt

- data/profile_instr_24_0.txt

--online オプション

aiesimulator --pkg-dir=Work --input-dir=data --output-dir=data --online Running AIE Simulator in Online mode... [INFO]: If you are running trace or profile, Xilinx recommends to use --xlopt=0. This will give a greater visibility into the design. One can verify --xlopt level in the aiecompiler command line. AIEsim feature license is found.

下記のところで、tmp.vcd.vcd という VCD ファイルを生成しています。

IP-INFO: [ps_i4_ps_main] IP started. Info: (I702) default timescale unit used for tracing: 1 ps (tmp.vcd.vcd) Open VCD pipe: /tmp/vcd_fifo_812e0c7b-1b69-438d-bbf9-b6013a45431d VCD Pipe id=42 Loading elfs of graph graph...

下記のファイルを生成されました。hwanalyze.log と tmp.vcd.vcd のファイルサイズは、0 です。

- hwanalyze.log

- tmp.vcd.vcd

- vcdanalyze.log

cat vcdanalyze.log AI Engine Performance Analysis Tool

また、trdata.aiesim ディレクトリの下にファイルが生成されました。

ls trdata.aiesim/ ctf data.xml events.txt function.name.json function.xml system.xml

--online オプションと合わせて、-wdb -ctf オプションを追加すると、Xilinx の xsim の波形フォーマットのデータベースを使うようです。

aiesimulator --pkg-dir=Work --input-dir=data --output-dir=data --online -wdb -ctf

- system.wcfg

- system.wdb

- system_flat.wcfg

xsim コマンドを --gui オプションにて、波形ファイル (system.wdb) を表示できます。

source ${VIVADO_HOME}/settings64.sh

xsim --gui system.wdb

また、vitis_analyzer コマンドを起動し、Trace の部分が下記のようになりました。

vitis_analyzer data/default.aierun_summary

aiesimulator.log の中を覗いています

cat aiesimulator.log 13:09:41.879550 [ info] @ -nan / aiesimulator.set_simulation_flags : Set work_dir to: data 13:09:41.883232 [ info] @ -nan / aiesimulator.set_simulation_flags : Set pkg_dir to: Work 13:09:41.883429 [ info] @ -nan / aiesimulator.set_simulation_flags : Set ess_debug to: 0 13:09:41.883595 [ info] @ -nan / aiesimulator.set_simulation_flags : Set debug_axi_mm to: false 13:09:41.883794 [ info] @ -nan / aiesimulator.set_simulation_flags : Simumation End wait time: 10 13:09:41.886716 [ info] @ -nan / aiesimulator.set_aiearch_version : Set ARCH to: aie 13:09:41.888781 [ info] @ -nan / aiesimulator.device_cfg_init : Loading device config from: /mnt/usb/XILINX/Vivado/2022.1/Vitis/2022.1/aietools/data/devices/VC1902.json 13:09:41.954665 [ info] @ -nan / aiesimulator.read_aiesim_config_json : Set physical device to: xcvc1902-vsva2197-1LP-e-S-es1 13:09:41.954891 [ info] @ -nan / aiesimulator.read_aiesim_config_json : AIE Frequencey: 1e+09 13:09:41.968703 [ info] @ -nan / tl.pl.ip_modules_0.IPModule : Loading IP lib: /mnt/usb/XILINX/Vivado/2022.1/Vitis/2022.1/aietools/data/pl_fileio/libpl_sender.so 13:09:41.973769 [ info] @ -nan / tl.pl.ip_modules_1.IPModule : Loading IP lib: /mnt/usb/XILINX/Vivado/2022.1/Vitis/2022.1/aietools/data/pl_fileio/libpl_sender.so 13:09:41.975367 [ info] @ -nan / tl.pl.ip_modules_2.IPModule : Loading IP lib: /mnt/usb/XILINX/Vivado/2022.1/Vitis/2022.1/aietools/data/pl_fileio/libpl_receiver.so 13:09:41.982753 [ info] @ -nan / tl.pl.ip_modules_3.IPModule : Loading IP lib: Work/ps/c_rts/systemC/generated-objects/ps_i4.so 13:09:42.064498 [ info] @ -nan / tl.pl.ProgrammableLogic : PL IP block has 32-bit output fifo (do) 13:09:42.064977 [ info] @ -nan / tl.pl.ProgrammableLogic : Conneced IP i1 do(32bit out) to ME stream 193. 13:09:42.065216 [ info] @ -nan / tl.pl.ProgrammableLogic : PL IP block has 32-bit output fifo (do) 13:09:42.065520 [ info] @ -nan / tl.pl.ProgrammableLogic : Conneced IP i2 do(32bit out) to ME stream 194. 13:09:42.065770 [ info] @ -nan / tl.pl.ProgrammableLogic : PL IP block has 32-bit input fifo (di) 13:09:42.065992 [ info] @ -nan / tl.pl.ProgrammableLogic : Connected ME stream 145 to IP i3 di(32bit in). 13:10:19.426071 [ info] @ 0 / aiesimulator.me_iss_start : ISS start... 13:10:19.426115 [ info] @ 0 / main.sc_main : About to sc_start ess 13:10:19.426361 [warning] @ 0 / aiesimulator::set_no_gated_clk.set_no_gated_clk: TCL interface disabled. 13:10:21.098345 [warning] @ 457 / SidebandCommands main_rts.ess_WriteCmd : TCL interface disabled. 13:10:31.959526 [warning] @ 24823 / Interpreter.request_profiles : Tcl interface disabled, not requesting profiles. 13:10:31.959736 [warning] @ 24823 / Interpreter.request_profiles : Tcl interface disabled, not requesting profiles. 13:10:31.959988 [warning] @ 24824 / interpreter::set_gated_clk.kill_simulator: TCL interface disabled. 13:10:31.960249 [ trace] @ 24824 / main.commandline_thread_process : End of commandline parser run. 13:10:32.059148 [ info] @ 24824 / main.sc_main : Simulation finished. 13:11:53.870596 [ info] @ 24824 / main.final_cleanup : Sim result: 0

下記のように、IP の ライブラリをロードしています。

[ info] @ -nan / tl.pl.ip_modules_0.IPModule : Loading IP lib: /mnt/usb/XILINX/Vivado/2022.1/Vitis/2022.1/aietools/data/pl_fileio/libpl_sender.so [ info] @ -nan / tl.pl.ip_modules_1.IPModule : Loading IP lib: /mnt/usb/XILINX/Vivado/2022.1/Vitis/2022.1/aietools/data/pl_fileio/libpl_sender.so [ info] @ -nan / tl.pl.ip_modules_2.IPModule : Loading IP lib: /mnt/usb/XILINX/Vivado/2022.1/Vitis/2022.1/aietools/data/pl_fileio/libpl_receiver.so [ info] @ -nan / tl.pl.ip_modules_3.IPModule : Loading IP lib: Work/ps/c_rts/systemC/generated-objects/ps_i4.so

Work/ps/c_rts/systemC/generated-objects/ps_i4.so は、(その4)でみてみました。

- aietools/data/pl_fileio/libpl_sender.so

- aietools/data/pl_fileio/libpl_receiver.so

は、Work/config/scsim_config.json の pl_ip_block で、

- 入力データ(その1)用 : input0.txt => data/pl_fileio/libpl_sender.so

- 入力データ(その2)用 : input1.txt => data/pl_fileio/libpl_sender.so

- 出力データ用 : output.txt => data/pl_fileio/libpl_receiver.so

"pl_ip_block": [

{

"name": "i1",

"arguments": [

"input0.txt",

"32",

"32",

"1",

"0",

"0"

],

"ip": "release",

"lib_path": "data/pl_fileio/libpl_sender.so",

"pl_freq": 250000000.0,

"axi_stream": [

{

"port_name": "do",

"column": 24,

"stream_id": 1,

"direction": "pl_to_me",

"bus_width": 32

}

],

"event_bus": []

},

{

"name": "i2",

"arguments": [

"input1.txt",

"32",

"32",

"1",

"0",

"0"

],

"ip": "release",

"lib_path": "data/pl_fileio/libpl_sender.so",

"pl_freq": 250000000.0,

"axi_stream": [

{

"port_name": "do",

"column": 24,

"stream_id": 2,

"direction": "pl_to_me",

"bus_width": 32

}

],

"event_bus": []

},

{

"name": "i3",

"arguments": [

"output.txt",

"32",

"32",

"1",

"0",

"0"

],

"ip": "release",

"lib_path": "data/pl_fileio/libpl_receiver.so",

"pl_freq": 250000000.0,

"axi_stream": [

{

"port_name": "di",

"column": 24,

"stream_id": 1,

"direction": "me_to_pl",

"bus_width": 32

}

],

"event_bus": []

},

13:09:42.064498 [ info] @ -nan / tl.pl.ProgrammableLogic : PL IP block has 32-bit output fifo (do) 13:09:42.064977 [ info] @ -nan / tl.pl.ProgrammableLogic : Conneced IP i1 do(32bit out) to ME stream 193. 13:09:42.065216 [ info] @ -nan / tl.pl.ProgrammableLogic : PL IP block has 32-bit output fifo (do) 13:09:42.065520 [ info] @ -nan / tl.pl.ProgrammableLogic : Conneced IP i2 do(32bit out) to ME stream 194. 13:09:42.065770 [ info] @ -nan / tl.pl.ProgrammableLogic : PL IP block has 32-bit input fifo (di) 13:09:42.065992 [ info] @ -nan / tl.pl.ProgrammableLogic : Connected ME stream 145 to IP i3 di(32bit in).

上記の部分では、下記の aiesimulator のログファイルに対応する部分ですね。上記の data/pl_fileio/libpl_sender.so と data/pl_fileio/libpl_receiver.so との接続部分っぽいですね。

- PL IP block has 32-bit output fifo (do) => Conneced IP i1 do(32bit out) to ME stream 193

- PL IP block has 32-bit output fifo (do) => Conneced IP i2 do(32bit out) to ME stream 194

- PL IP block has 32-bit input fifo (di) => Connected ME stream 145 to IP i3 di(32bit in)

--------------------------------------------------------------------------------------------------

SLAVE STREAM INFO: | Port Name | Port Width | Stream Type | Channel Index

| S00_AXIS | 32 | PL STREAM | 193

| S01_AXIS | 32 | PL STREAM | 194

--------------------------------------------------------------------------------------------------

--------------------------------------------------------------------------------------------------

MASTER STREAM INFO: | Port Name | Port Width | Stream Type | Channel Index

| M00_AXIS | 32 | PL STREAM | 145

--------------------------------------------------------------------------------------------------

下記の部分からTCLファイル関連のログが出ていますね。

[ info] @ 0 / aiesimulator.me_iss_start : ISS start... [ info] @ 0 / main.sc_main : About to sc_start ess [warning] @ 0 / aiesimulator::set_no_gated_clk.set_no_gated_clk: TCL interface disabled. [warning] @ 457 / SidebandCommands main_rts.ess_WriteCmd : TCL interface disabled. [warning] @ 24823 / Interpreter.request_profiles : Tcl interface disabled, not requesting profiles. [warning] @ 24823 / Interpreter.request_profiles : Tcl interface disabled, not requesting profiles. [warning] @ 24824 / interpreter::set_gated_clk.kill_simulator: TCL interface disabled. [ trace] @ 24824 / main.commandline_thread_process : End of commandline parser run. [ info] @ 24824 / main.sc_main : Simulation finished. [ info] @ 24824 / main.final_cleanup : Sim result: 0

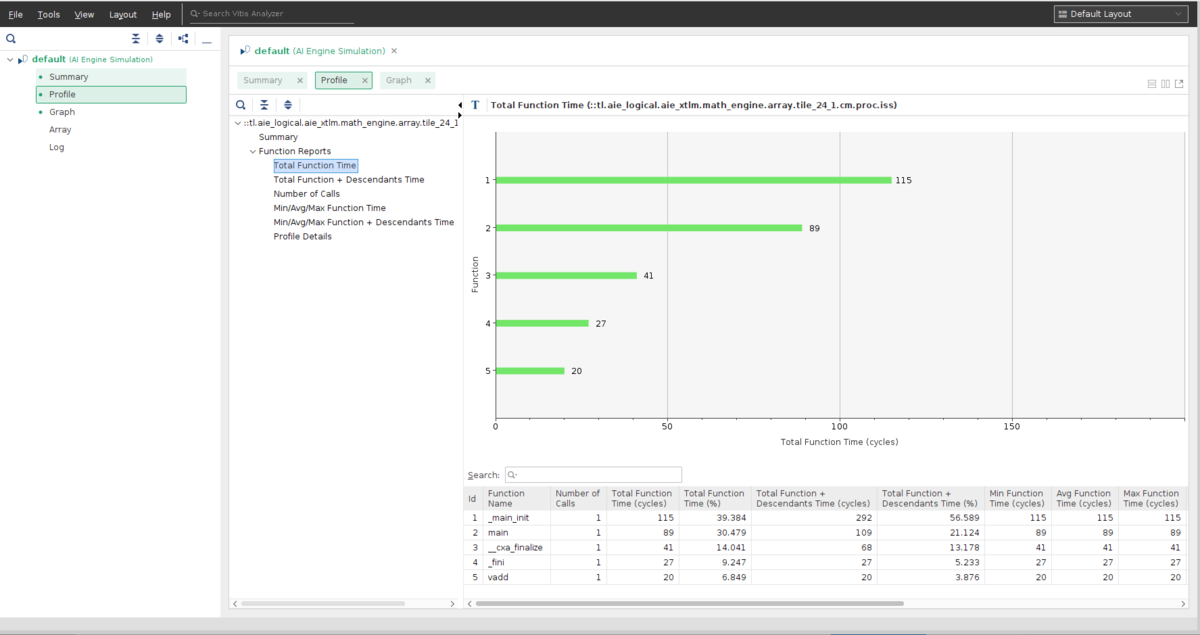

vitis_analyzer コマンド

vitis_analyzer コマンドにて、下記のようにレポートが見られるようです。

vitis_analyzer data/default.aierun_summary

Profile の部分です。

Graph の部分です。

Array の部分です。

おわりに

Xilinx AI Engine の シミュレータ (aiesim www.acri.c.titech.ac.jp

ulator) を動かしてみました。

この aiesimulator は、AI Engine 部分のシミュレータなので、実機では、ホストからの制御等のプログラムは別途必要です。この部分については、下記の記事の後半に書いてあるので、覗いてみてください。