はじめに

Moore's Law Is Deadの下記の動画「Intel Nova Lake Full Leak: 52C Pictured, 288MB L3, Hammer Lake on LGA 1954!」にて、Nova Lake の詳細が出ています。

その中で、来年出てくる Nova Lake の CPU die の L3 cache は、144MB ととてつもない容量のようです。

Nova Lake

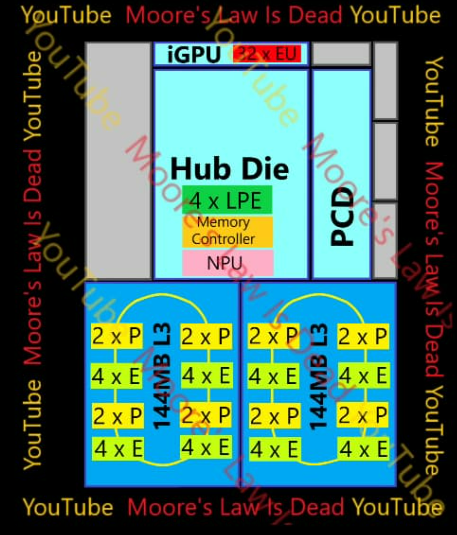

下図は、上記の動画から、説明のために引用します。Nova Lake の full 実装のもののようです。

- CPU die x 2 : 8P16E bLLC (big Last Level Cache)

- Hub die : North Bridge IP、メディアエンジン、NPU、メモリコントローラー、4LPE

- iGPU die : Xe3 /Celestial 32EU

- PCD (latform Controller die) : South Bridge IP、ディスプレイ出力、PCIe

の5つの Die から構成されるようです。

下記のブログでは、Meteor Lake / Arrow Lake の die shot を紹介していますが、

- CPU die :

- SoC die :

- iGPU die :

- I/O die :

の 4 die 構成になっています。Nova Lake も基本的には同じ構成ですね。ただし、CPU die が 2 個になっています。

Nova Lake でも CPU die が 1個のケースもあると思います。Hub die は共用だと思うので、1つのCPU die と 2つのCPU die の接続がどうなっているのかが気になります。

Hub die の面積(CPU dieなどと接続するための辺が必要なので)が大きくなるんじゃないでしょうか? その分、色々な機能が入れられるというメリットもあります(コストアップにはなる)

おわりに

上記の動画によると、

- Flagship (TSMC N2P): 16P32E4LPE=52コア、2CPUタイル。各CPUタイルに144MBのbLLCを内蔵し、bLLC (L3キャッシュ)の合計は288MB

- Premium Gaming (TSMC N2P): 8P16E4LPE=28コア、144MB bLLC (L3キャッシュ)

- Main Stream (TSMC N2P): 8P16E4LPE=28コア、L3キャッシュは36MB

- Budget TSMC N2P): 4P8E4LP=16コア、L3は18MB

- Entry (Intel 18A): 4P0E4LPE=8コア、L3は12MB

の5種類があるようですが、Entry だけが、Intel 18A なのは何で?と思いました。 Entry も CPU die だけになるんでしょうか。