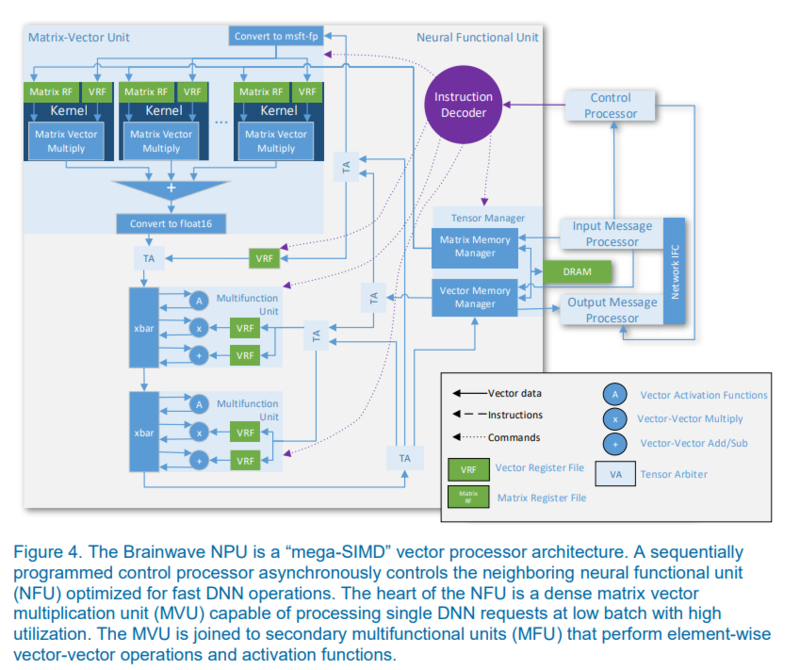

制御プロセッサには、NIOS使っています。このNIOSを使っているのがポイントなのかな?

この制御プロセッサからの命令を Instruction Decoder で

Matrix-Vector Unitや Multifunction Unit、Tensor Manager に振り分けています。

この制御プロセッサからの命令を Instruction Decoder で

Matrix-Vector Unitや Multifunction Unit、Tensor Manager に振り分けています。

Neural Function Unit 内に、Matrix-Vector Unitと2つの Multifunction Unit、それと、Tensor Manager。

Tensor Managerは、Input Message ProcessorからTensorやVectorを受け取り、

処理後の Vector を Output Message Processor に書き込みます。

Tensor Managerは、Input Message ProcessorからTensorやVectorを受け取り、

処理後の Vector を Output Message Processor に書き込みます。