はじめに

Intel PowerViaを使ったテストチップに関連するTweetが流れてきたので、記録として残します。

#VLSI2023 Highlight paper T1-1 “E-Core Implementation in Intel 4 with PowerVia (Backside Power) Technology” – Intel Corp.

— IEEE Symposium on VLSI Technology and Circuits (@VLSI_2023) 2023年5月2日

Intel reports a high-yielding backside power delivery technology, PowerVia Technology*, and Intel E-Core Implementation in PowerVia Technology. pic.twitter.com/0us9rbUvQr

Intel PowerVia とは?

下記の記事に、Intel PowerVia の情報が載っています。

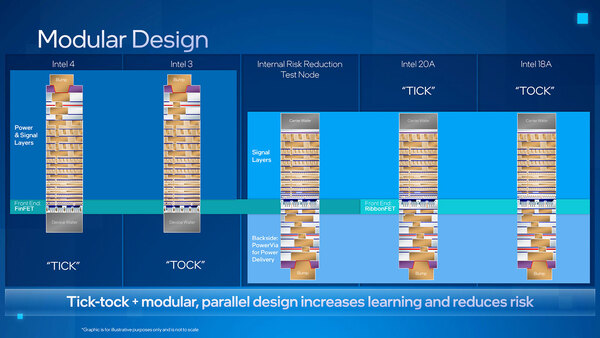

下図は上記のサイトから説明のために引用します。

Intel 20A にて、PowerVia を導入し、Intel 18A で第二世代PowerViaを導入する感じのようです。Intel 20A の前に、Test chip を作ると。

Intel PowerVia の Test chip

今回、Twitter に流れてきたのは、この test chip のお話のようです。E-Core CPUにて、PowerViaを使ったと。

Intel's PowerVia enabled an over 90% standard cell utilization in large portions of the core, while also providing a more than 5% clock speed improvement due to reduced IR drop.

電源は裏側、信号は表側になるようですが、Package にする場合はどうなるんでしょうか?

上記のPackageの写真は、Pin側のようですが、die が見えます。。。

VLSI Symposium の資料

下記のTHE NEXTPLATFORMの記事は、来週のVLSI Symposiumの資料をまとめたものです。

下図のその中の一部です。説明のために引用します。PowerRailとPowerViaの比較です。

おわりに

PowerVia になった場合、放熱って、どうするんでしょうか?

参考記事

追記)、2023.07.16