はじめに

Xに下記の投稿が流れてきました。

C2C latency for the @Qualcomm @Snapdragon X Elite (X1E-80-100) with 12 cores that shows the three quad core cluster and quite some significant high latencies between those.

— Andreas Schilling 🇺🇦 🇮🇱 (@aschilling) 2024年9月19日

But as we learned with Ryzen 9000: That doesn't mean much and can be a conscious design decission. pic.twitter.com/zS159lOUfu

画像が無くなると説明できないので、画像を説明のために引用します。

これを見る限り、3つのブロックになっているっぽいです。ブロック間での アクセスレイテンシーは同じぐらいですが、

- 同一ブロック内

- 他のブロック、その1

- 他のブロック、その2

そのブロック、その1、その2では、何となく、値が違いますね。。。

X Eliteって、X1E-80-100 という型番なんですね。

Die shot を眺めてみる

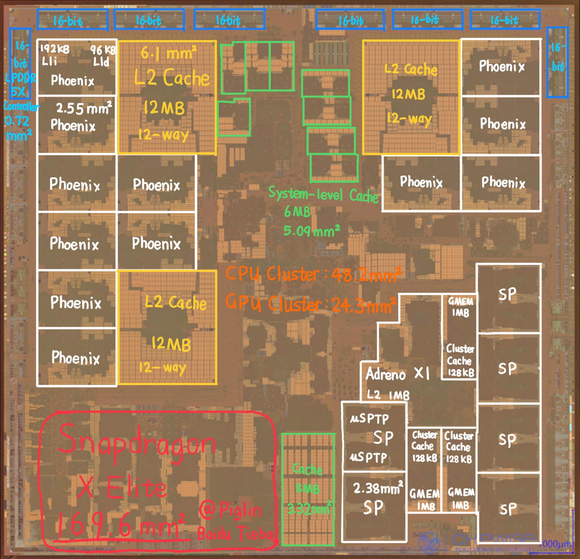

The die shot of Snapdragon X Elite have been revealed by Piglin, a user active in Baidu Tieba!

— Quadrans Muralis (@QaM_Section31) 2024年9月28日

Die size : 169.6 mm^2

Reference) Apple M4 : 165.9 mm^2

SOURCE : https://t.co/mKDBdQvNCF pic.twitter.com/zRM4TjHUS5

画像が無くなると説明できないので、画像を説明のために引用します。

この DIe shot をみると

- 左側に2ブロック

- 右側に1ブロック

あります。

によって、ちょっと時間が違うんでは?

と思います。

おわりに

各ブロック内には、L2 Cache (12MB) があります。そして、System Level Cache が 6MB 。。。あれ、L2 Cache より小さいですね。。。。

このような構成でも、性能出るのですかね。

最初のC2C Latencyの図(表)を見て、なんでだろうと思いましたが、Die shot を見て、その理由が分かりました。

あー、すっきり、しました。。。