@Vengineerの戯言 : Twitter

SystemVerilogの世界へようこそ、すべては、SystemC v0.9公開から始まった

Cerebras Systemsの職募集で気になったもがこちら。

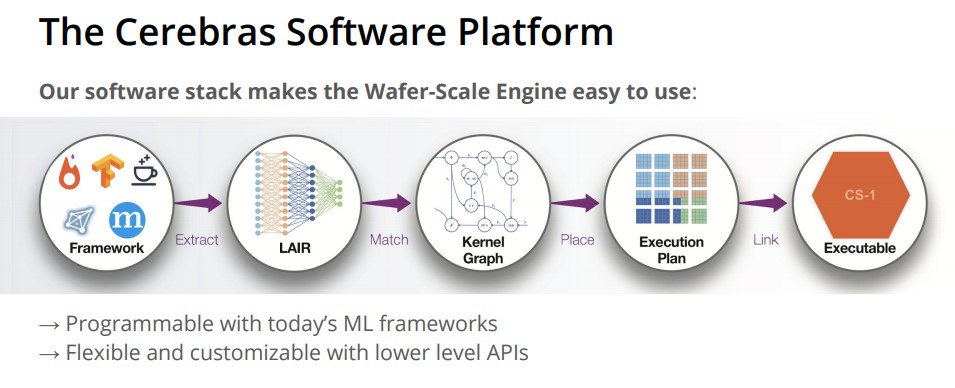

何故、この職が必要なのかは、下記のブログの中にURLがSC19での講演資料

の6頁目(下図、引用します)の図の右側から2つ目の「Execution Plan」のためのPlaceです。つまり、WSEの中でモデルの配置配線をやるのです。

半導体開発やFPGA開発におけるPlace & Routeのようだと思います。

Cerebrasの場合、このPlace & Routeが、性能や容量(モデルの規模)に大きな影響を与えると思います。

何れ無くなってしまうので、全文、引用します。

Place & Route Engineer

Cerebras is developing a radically new chip and system to dramatically accelerate deep learning applications. Our system runs training and inference workloads orders of magnitude faster than contemporary machines, fundamentally changing the way ML researchers work and pursue AI innovation.We are innovating at every level of the stack – from chip, to microcode, to power delivery and cooling, to new algorithms and network architectures at the cutting edge of ML research. Our fully-integrated system delivers unprecedented performance because it is built from the ground up for the deep learning workload.

Cerebras is building a team of exceptional people to work together on big problems. Join us!

The Role

As a Place & Route Engineer, you will directly impact the performance at which deep learning models are executed on hardware and be responsible for enabling next-generation AI applications that require substantial computational capabilities.In this position, you will develop algorithms for partitioning, placement, floor planning, and routing of communication for dataflow graphs on a massively parallel, multi-core architecture.

Specific responsibilities may include:

Model the allocation of compute, communication, and memory resources as optimization problems.

Implement mathematical models in C++ or Python using discrete optimization techniques and standard libraries and packages.

Measure, analyze, and optimize quality of results produced by mathematical models and their implementations.

Integrate successful models into production software stack.

Skills & Qualifications

PhD or Master degree in Computer Science, Computer Engineering, Electrical Engineering, Applied Mathematics, or related field

3+ years experience in developing physical design, technology mapping, and place & route tools for FPGA or ASIC designs, or related experience

Expert knowledge of linear programming, constraint solvers, and combinatorial optimization

Experience modeling optimization problems using simulated annealing, genetic programming, dynamic programming

Hands on experience in deploying graph algorithms

Strong proficiency in C/C++ or other language for designing large, performant systems.

Passion for high quality and easily maintainable software development practices including coding conventions, code reviews, and testing.

Familiarity with Python or other scripting language.

The ability to operate at multiple levels of abstraction in the software stack.

Successful candidates need to have demonstrated the ability to both solve challenging algorithmic problems and implement them cleanly in performant code.The Team

The Place & Route team designs a backend system that transforms an abstract computational graph to a specific plan that can be run on our hardware. Our team consists of highly skilled PhDs and engineers with strong backgrounds in parallel computing, graph algorithms, constrained optimization, and machine learning, with many combined years of industry experience. We are looking to grow our team with highly motivated individuals eager to solve challenging algorithmic problems and implement their methods, following sound engineering principles.Location

Our cozy and well-appointed headquarters are in the heart of Silicon Valley near downtown Los Altos, California.