はじめに

Intel Clearwater Forest の詳細が出てきたので、記録に残します。

これ以降の図は、上記の記事から説明のために引用します。

Intel Clearwater Forest

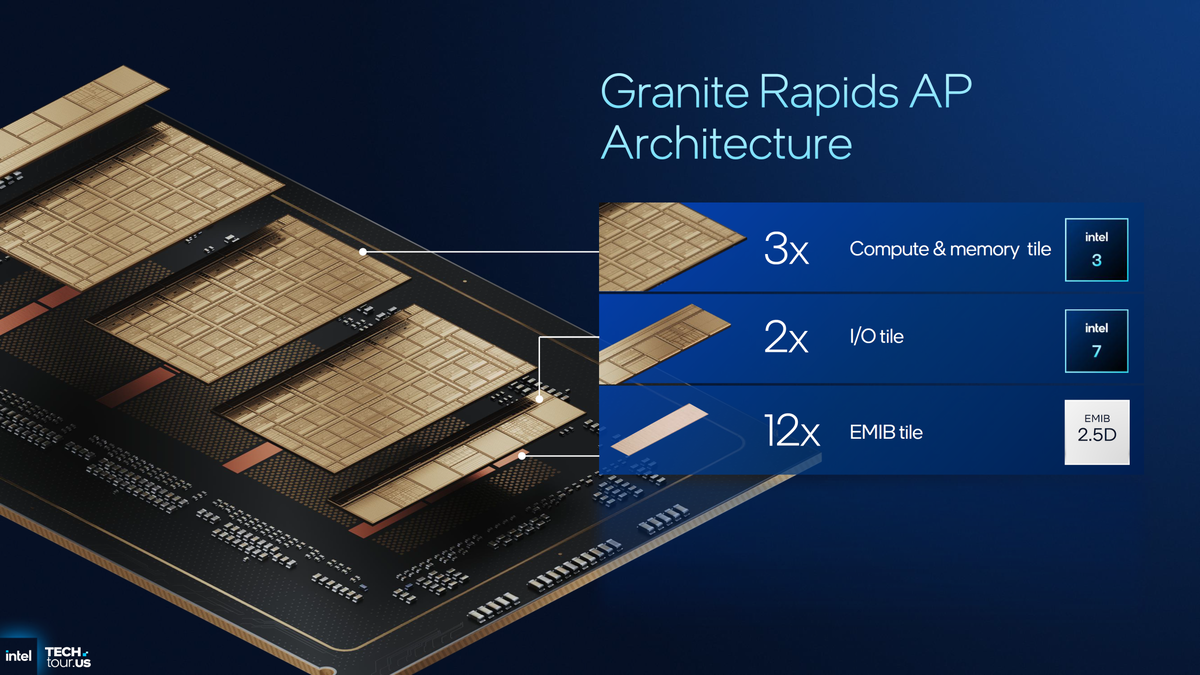

Granite Rapids AP の アーキテクチャが下図です。

これに対して、Clearwater Forest は、

- 12x Compute tile : intel 18A

- 3x Active base tile : intel 3

- 2x I/O tile : intel 7

- 12x : EMIB tile : EMB 2.5D

Granite Rapids => Clearwater Forest では、

- 3x Compute & Memory tile : intel 3

が

になった。

Compute と Memory を分離。Memory は、intel 3 のままで、Compute を intel 18A に。

この部分の詳細が下記の図。

この部分の詳細は、下記のPC Watch の記事にありました。説明のために引用します。

https://pc.watch.impress.co.jp/docs/news/2053437.html

- 192MB : Last level cache per base tile

- 48MB : last level cache per compute tile

- 4 : DDR5 memoy channels per base tile

- 6 : Module per tile

- 4 : Cores per module

- 24 : Darkmont E-cores per compute tile

- 4MB : Shard L2 cache per module

48MB L3 Cache で、24 コア。1コアで2MB.

AMD 第5世代 EPYC (192コア)では、384MBのL3 Cache。1コアで2MB。

同じ。

おわりに

- Intel Clearwater Forest は、24コア x 4 x 3 = 288コアで、576MBのL3 Cache

- AMD 第5世代 EPYC (192コア)では、384MBのL3 Cache

やっと、AMDに追いついた感じですかね。。。