はじめに

Xの投稿に流れてきた、AMD MI350 の情報について、記録しておきます。

tom's HARDWARE がまとめてくれています。

AMD MI350

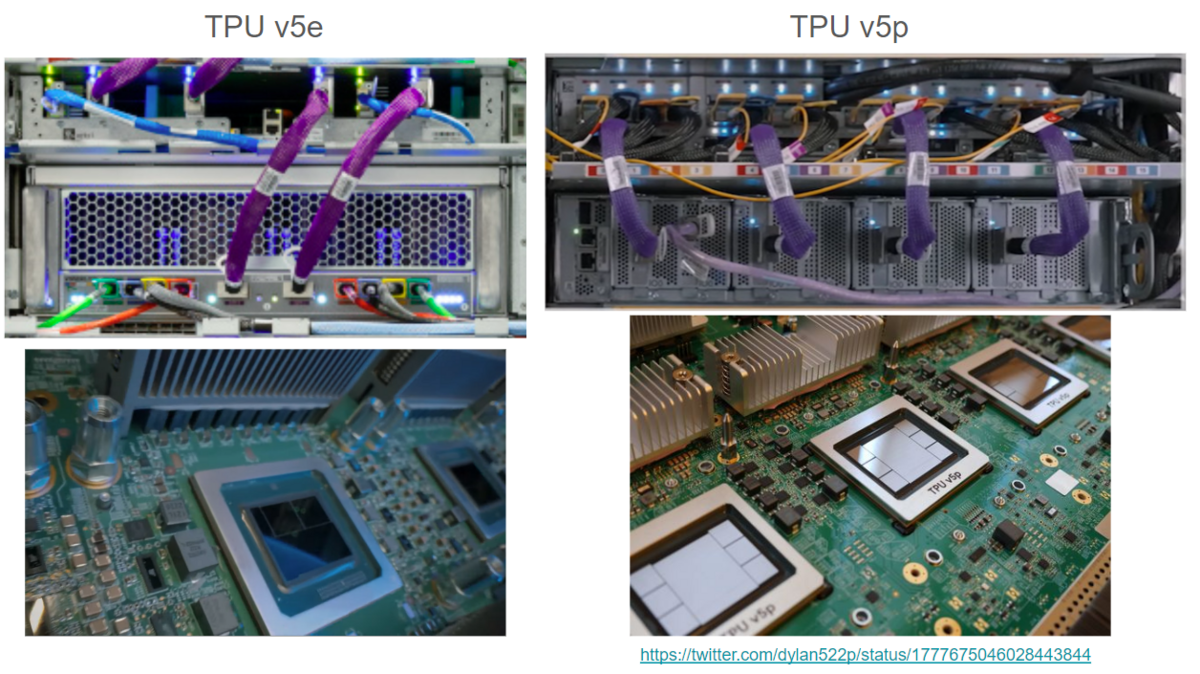

どうやれ、TSMC 4nm で 2024/H2 に出てくるようです。

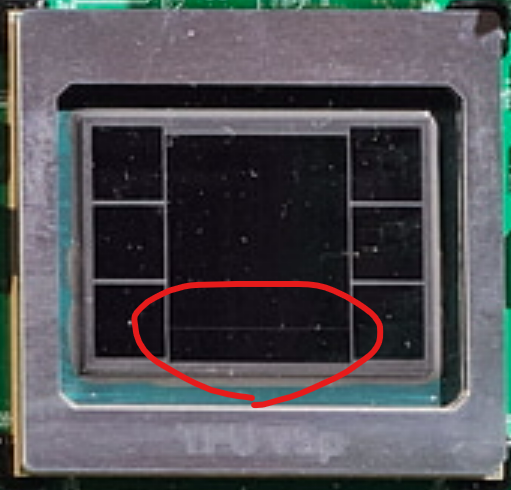

MI300が TSMC 5nm/6nm だったので、Compute Die を 4nm にするのでしょうかね。。。

5nm => 4nm になって、SRAMが小さくならないので、Logic部を増やすか、動作周波数を上げる感じですかね。。。

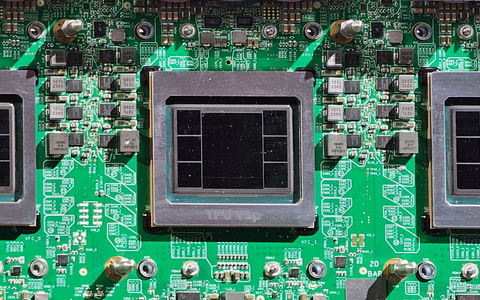

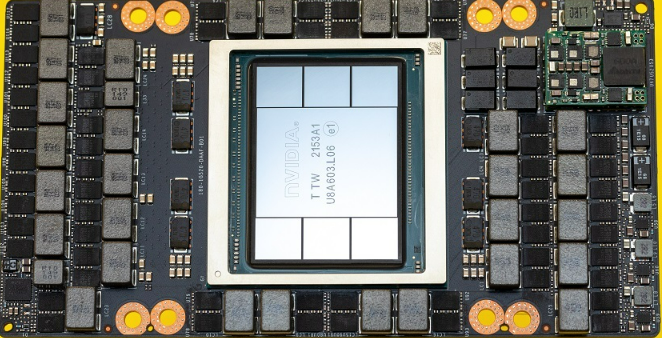

ちなみに、MI300X は下記のようになっています。

- MI300X

- 8 x XCD (38 CUs)

- 4 x IOD

- 8 x HBM3 (192GB/12H)

- 256MB Infinity Cache

- 3.5D packaging

おわりに

なんで、MI350 を出すんでしょうかね。。。

IODが同じだと、HBM3も同じような感じだと思うのですが。。。。

あ、もしかしたら、MI250 の 6nm を MI350 で 4nm にするということ?

あ、MI250では、HBM x 4 で die が2個。。となると、MI250 では、HBM x 6 で die が 2個とか。。。メモリたくさん作戦?

24 GB x 12 = 288GB .