Vengineerの戯言 : Twitter

SystemVerilogの世界へようこそ、すべては、SystemC v0.9公開から始まった

はじめに、

今日は、昨日、Twitterで告知したように、SiMa.ai の MLSoC について、まとめてみました。

明日は、https://t.co/Rx6sAAAJg4 の MLSoC について

— Vengineer@ (@Vengineer) 2021年1月9日

まとめたいと思っています。

Arm Cortex-A65を搭載した MLSoCは、16nmに実装され、カメラ入力としてMIPIが4組、10GbEが2組、PCIe Gen4 x16、MLAとして Mosaicを一基搭載しています。

昨日の夜、Youtubeでビデオを観て、今日、このブログにまとめるために、再度、じっくり観て、聴いたら、昨日観たより多くの情報を得ることができました。

SiMa.ai という会社は、何を作っているのか?

SiMa.ai という会社と SiMa.ai が何を開発しているのか SiMa.ai のサイトの中を見ていきます。

SiMa.ai のサイトをざっくと眺めてみる限り何を作っているかはよくわかりません。CEOは、KRISHNA RANGASAYEE さん。KRISHNA RANGASAYEE さんには、一度、Xilinxに居たときに MTG をした時があります。物静かで紳士的な方というのがその時のあたしの印象です。KRISHNA RANGASAYEE さんは、Xilinxを辞めた後、Groq に移りましたが、1年4カ月で Groqを辞め、Sima.ai の ほかのメンバーと一緒に創業し、CEO になっています。

SiMa.ai の サイトのアプリケーションのページを見てみると、次の3つをアプリケーションとして考えています。

- Untethered robots (<20W) <=> As opposed to 100-300W qith competing solutions)

- An all-electric vehicle world (<10W (L2+) and <100W (L4-5) <=> As opposed to 1000-3000W with competing solutions)

- Democratization of secure diagnostics in health care for all (5W for low ost and <50W for highest peformance <=> As opposed to 50-1000W with competing solutions)

競合に対して、消費電力が 1/10 程度で実装するというのがポイントっぽいです。

消費電力が少ないということなので、ハードウェア(半導体)を開発していると思うのですが、サイトにはそれらしきものがありません。

CAREERSのところに、募集しているポジションが見つかりました。いずれ無くなってしますので、魚拓を取りました。

ポジションの中には、下記のようなものがありますね。

- HARDWARE DESIGN VERIFICATION - INDIA

- HARDWARE DESIGN ENGINEER - INDIA

- CAMERA DSP and COMPUTER VISION DEVELOPMENT - INDIA

- SENIOR OPERATING SYSTEM and BUILD CONFIGURATION, SoC SW DEVELOPMENT - INDIA

- SENIOR DRIVER DEVELOPMENT ENGINEER, SoC SW DEVELOPMENT - INDIA

- DRIVER / OS DEVELOPEMT ENGINEER, SoC SW DEVELOPMENT

HARDWARE DESIGN ENGINEER の中を覗いてみました。

The Hardware Design Engineer will help develop the micro-architecture and design methodology for SiMa.ai’s MLSoC. Your responsibilities would include RTL coding, design and reviews, synthesis, static timing analysis and coverage analysis. This means working very closely with the Arch team, Verification team, back-end team as well as cross-functional teams. The primary design target is an SoC ASIC with ML being a key component.

どうやら、MLSoC というのを開発しているっぽいです。

HARDWARE VERIFICATION ENGINEER の中を覗いてみました。

As the Hardware Design Verification Engineer, you will help lead and develop the verification methodology for SiMa.ai’s MLSoC™. As the Lead, you will be responsible for developing test plans, testbenches, drivers, monitors and checkers/scoreboard, testcases, coverage analysis and simulation, verify the functionality, performance and other aspects of RTL designs including the block-level and chip/system level, emulation and validation support. You will work very closely with the Architecture, RTL/uArch, and cross-functional teams.

including the block-level and chip/system level, emulation and validation support. とありますので、DESIGN と VERIFICATION を完全に分けていますね。

CAMERA DSP and COMPUTER VISION DEVELOPMENT ということなので、MLSoC には Camera I/F と 処理には DSP がはいっているのが分かります。

SENIOR DRIVER DEVELOPMENT ENGINEER, SoC SW DEVELOPMENT では、

- Leveraging IP SW from Synopsys and ARM and integrate into MLSoC™ SW environment.

これで、IPは Synopsys と ARM から持ってくる。。

- Working with Zebu emulators.

- Working with Virtualizers.

emulator として、Synopsys の Zebu、Virtual Platform は Synopsys の Virtualizers を使う。

ここまでで、MLSoC の中には、Arm Cortex-AシリーズのCPUコアが入っているのが分かりますね。

- Bring up and Run Multiple Operating systems on the same Processor.

- Hardware communication between multiple cores.

- IPC communications between Multiple ARM processors.

- IPC communications between ARM and Non-ARM processors.

ここから、Arm Cortex-AシリーズのCPUコアはマルチコアで、ARMコアの他にも Non-ARM processors も搭載

- Hands-on experience developing firmware, boot code and SW using high performance 64 bit Arm processors.

ARM Cortex-Aシリーズは、64ビット。

- Hands-on experience developing drivers for SPI, I2C, USB, PCIe, MIPI interfaces.

ペリフェラルとしては、SPI, I2C, USB, PCIe, MIPI 、となると Camera I/F は、MIPI。

- Development experience with Embedded Linux (e.g. Yacto) and embedded RTOS (e.g. QNX) experience is highly desirable.

組み込みLinux は、Yacto ?たぶん、Yoctoだろう。組み込みRTOSは、QNXか。

ここまでに分かったこと。

MLSoC は、

- ARM Cortex-Aシリーズの64ビットのマルチコア

- Non-ARM processors

- SPI, I2C, USB, PCIe, MIPI

- Camera DSP

が搭載されている。これなら、普通の SoC っぽですね。

Google君に聞いたら、Cortex-A シリーズとしては、A65 を使っているようです。A65は、A Multithreaded DynamIQ CPUです。A5x/A7xはSingle Thread CPUコアですが、A65に dual thread なんですよ。

www.arm.com

講演ビデオを観て、内容をじっくり掘り下げる

ここからは、Youtubeに公開されている3本のビデオを観ていきます。

- 「The Linley Spring Processor Conference 2020」の「SiMa.ai: High Performance, Green Machine Learning for Embedded Edge Systems」

- 「The Linley Fall Processor Conference 2020」の 「SiMa.ai: Using a Machine-Learning SDK to Boost Performance/Watt in Edge-AI Systems」

- 「TVM Conf 2020」の「TVM Conf 2020 - Day 1 - Extending TVM to Support Custom ML Hardware」

これら3つのビデオをじっくり観、聴いたことにより、MLSoC の中の構造がより分かりました。また、MLSoC で動くディープラーニングフレームワークは、TVMでヘテロなハードウェアでどんな感じで動かしているかもわかりました。

さあ、ビデオをじっくり観、聴いていきましょう!

SiMa.ai の MLSoC の詳細については、「The Linley Spring Processor Conference 2020」の「SiMa.ai: High Performance, Green Machine Learning for Embedded Edge Systems」には初めて公開されました。

www.youtube.com

ここからは上記ビデオ内のスライドを見ていきます(引用します)

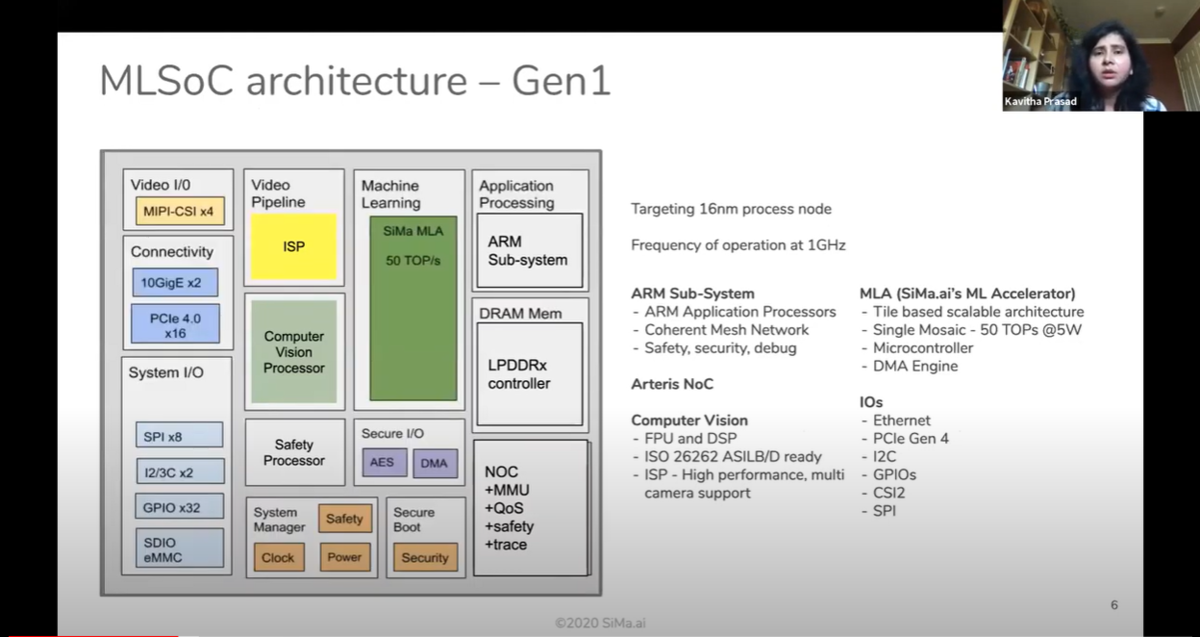

下図(3:55頃)は、MLSoC の説明

MLSoC architecture - Gen1 、Gen1 ということで、Gen2, Gen3 ... もあるのかな?

- Targeting 16nm

- 1GHz Operating Frequency

- Ariteris NoC

- Video I/O (MIPI-CSI x4)

- Connectivity (10GbE x2, PCIe 4.0 x16)

- System I/O (SPI x8, I2/3C x2 GPIO x32, SDIO/eMMC)

- Video Pipeline (ISP)

- Computer Vision Processor => FPU and DSP

- Machine Learning (SiMa MLA : 50 TOP/s)

- Safety Processor

- System Manager (Clock, Safety, Power)

- Secure Bool (Security)

- Secure I/O (AES, DMA)

- Application Processing (ARM Sub-system)

- DRAM Mem (LPDDRx controller)

- NOC (MMU/QoS/safety/trace) => Coherent Mesh Network

ブロック図を見る限り、MLA が追加された Camera 対応の SoC ですね。

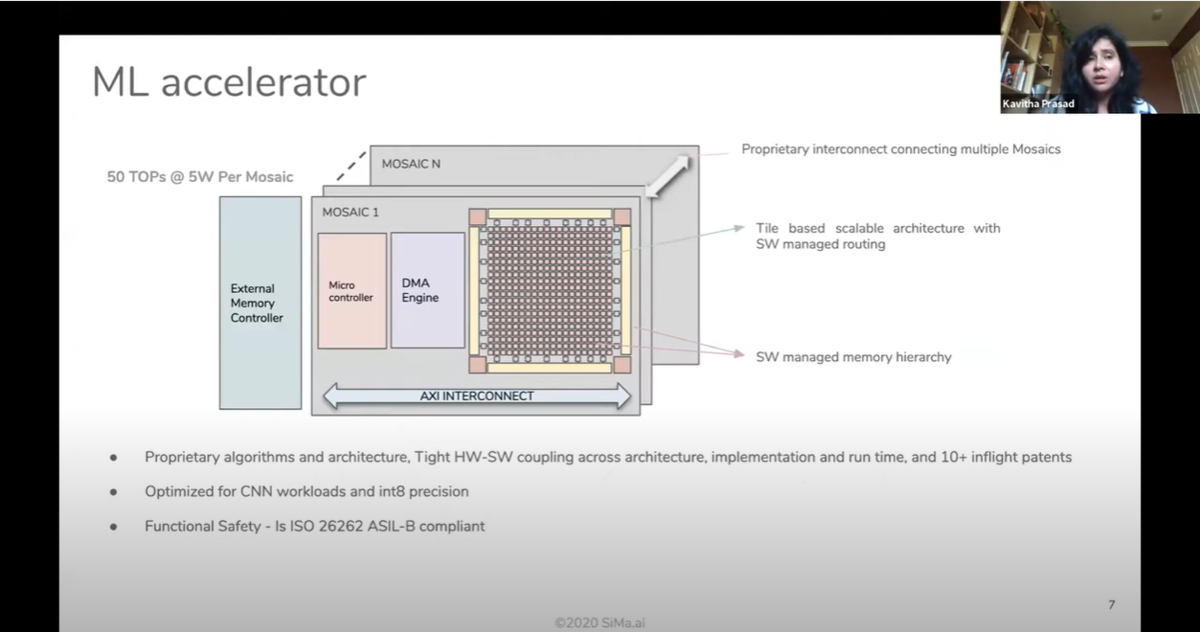

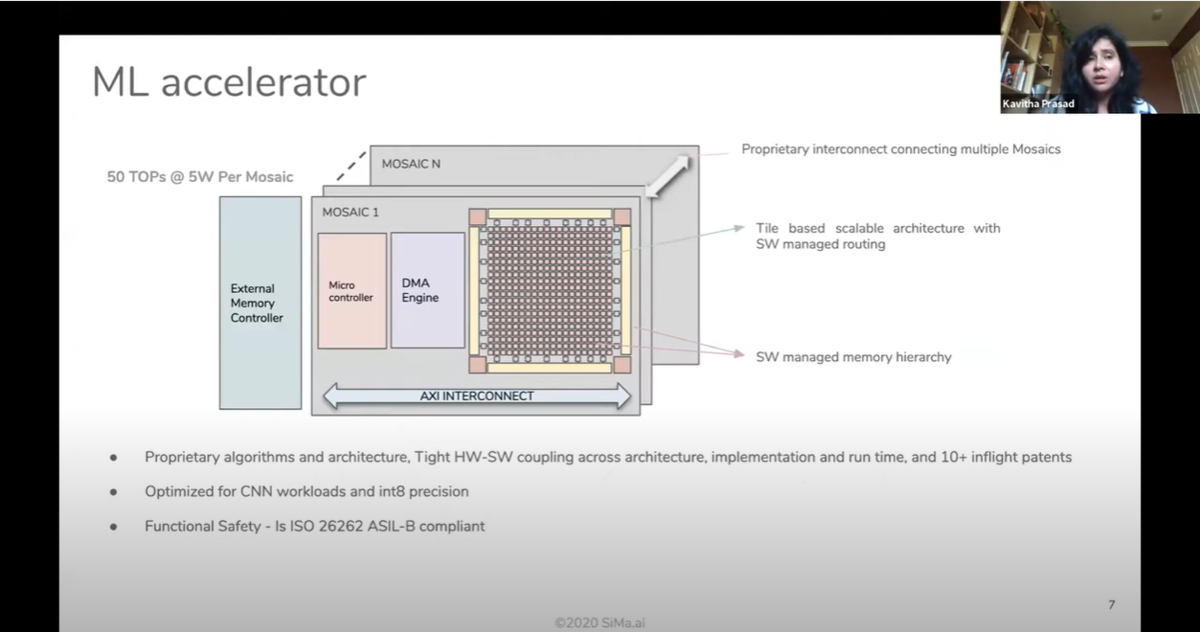

下図(6:38頃)は、ML accelerator の説明

ML accelerator は、MOSAIC という名前で、

- Micro controller

- DMA Engine

- Tile based scable architecture with SW managed routing

- SW managed memory hierachy

- Proprietary algorithms and architecture. Tight HW-SW coupling across architecture, implementaton and run time, and 10+ inflight patents

- Optimized for CNN workloads and int8 precision

- Functional Safety - is ISO 26262 ASIL-B compliant

タイルベースのプロセッサで、精度は 8bitのみ。データ移動は DMA にて行う

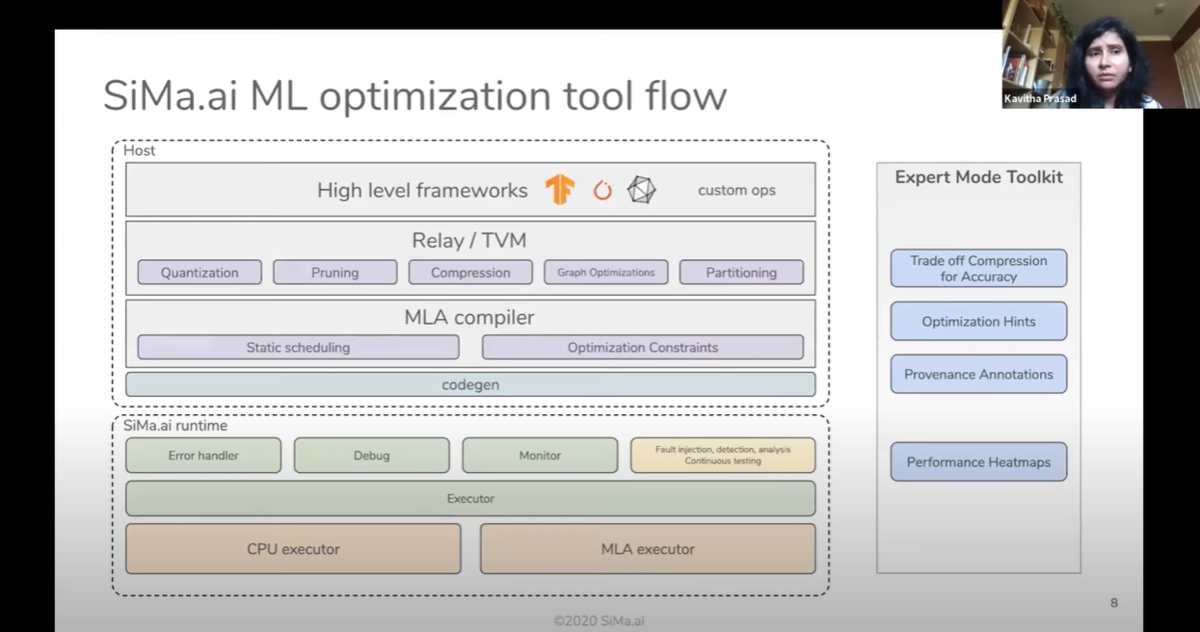

下図(8:28頃)は、ML optimization tool flow で、ディープラーニングのフレームワークは Relay/TVM ですね。Relay/TVM の下に MLA compiler として、

- Static scheduling

- Optimmization Constraints

- codegen

runtime として、

- Error handler

- Debug

- Monitor

- Fault injection, detection, analysis Continuous testing

- Executor (CPU executor / MLA executor)

次の講演ビデオは、「The Linley Fall Processor Conference 2020」の 「SiMa.ai: Using a Machine-Learning SDK to Boost Performance/Watt in Edge-AI Systems」

www.youtube.com

下図(2:15頃)では、SiMa.ai MLA SDK in Context

- Targeting 16nm

- 1GHz Operating Frequency

- LPDDRx (Q&A で、LPDDR4)

- On Chip Memory 4MB (これは初めて、Q&Aで汎用用途のSRAM)

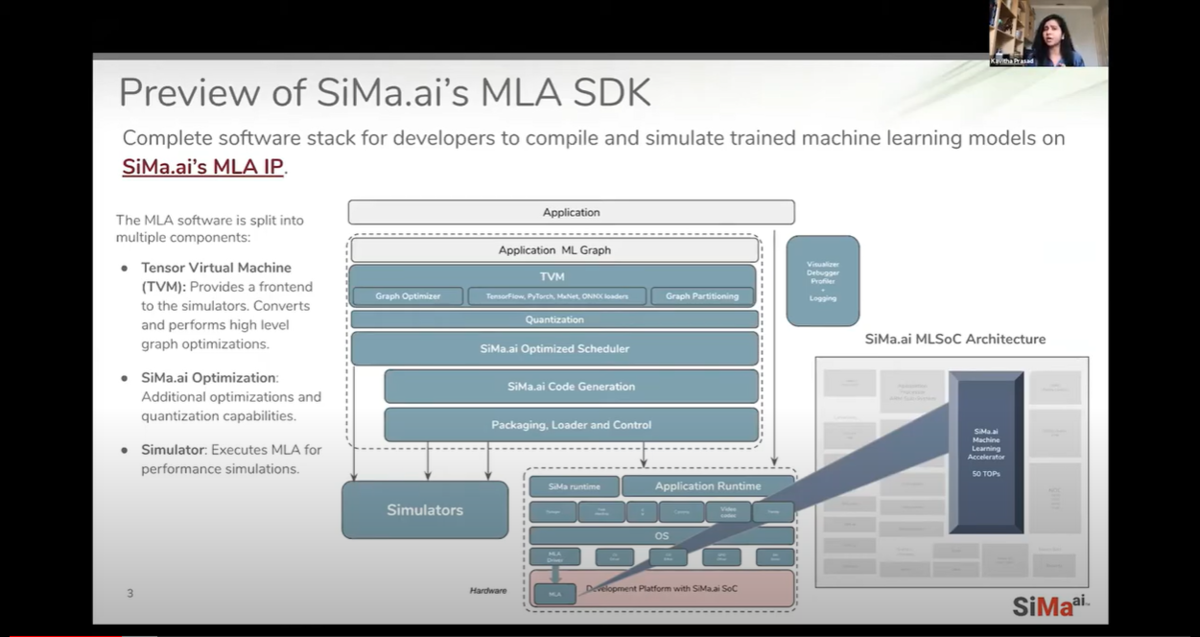

下図(2:48頃)では、Preview of SiMa.ai's MLA SDK

図の左下は、Simulators、右下がHardware。この Hardware の上の方に、SiMa runtime と Application Runtime とRuntime が 2つありますね。

これは、CAREERSのところにあった、

- IPC communications between ARM and Non-ARM processors.

- Development experience with Embedded Linux (e.g. Yacto) and embedded RTOS (e.g. QNX) experience is highly desirable.

から、SiMa runtime は、embedded RTOS (QNX) が動いている(QNXが動くコア)上で動いているんでしょうね。

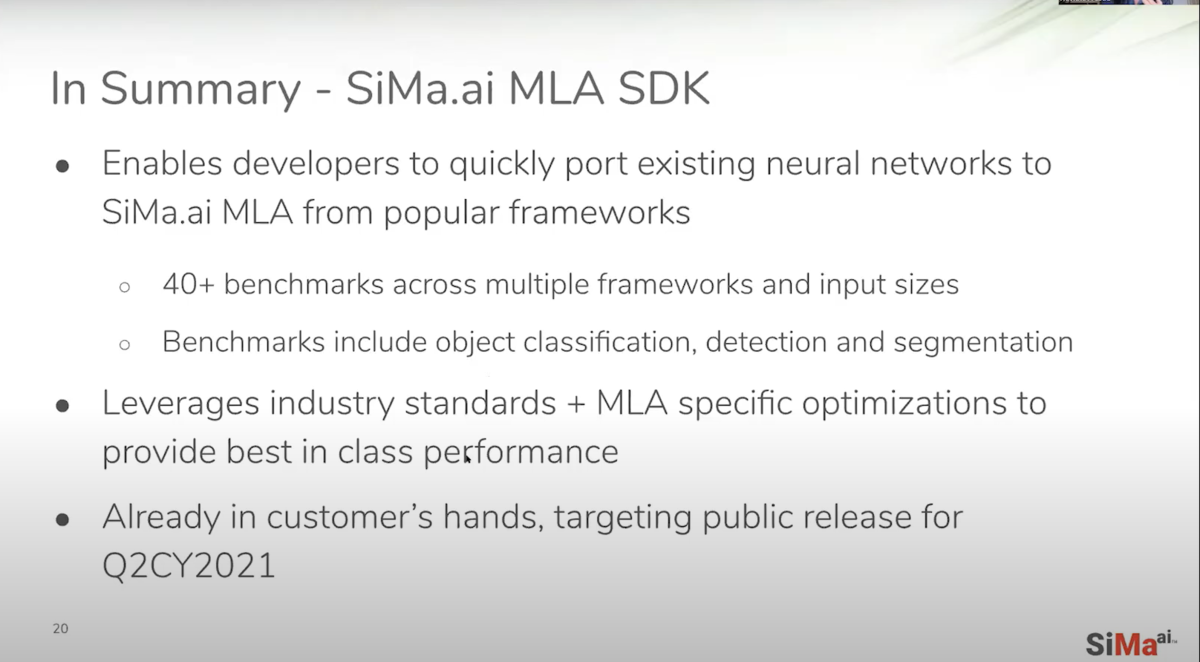

下図(13:31頃)では、SiMa.ai MLA SDK は、Q2CY2021 公開されるようです。

Q&Aでは、

- まだチップはできていなくて、Emulation (HW Emulator) での動作確認した

- Computer Vision 部は、Synopsys の EV74の ライセンスIPのようです

- メモリは、LPDDR4

- 汎用のSRAM 4MB。MLA用に20MB SRAM。

ということがわかりました。

最後のビデオは、TVM Conf 2020 - Day 1 - Extending TVM to Support Custom ML Hardware

www.youtube.com

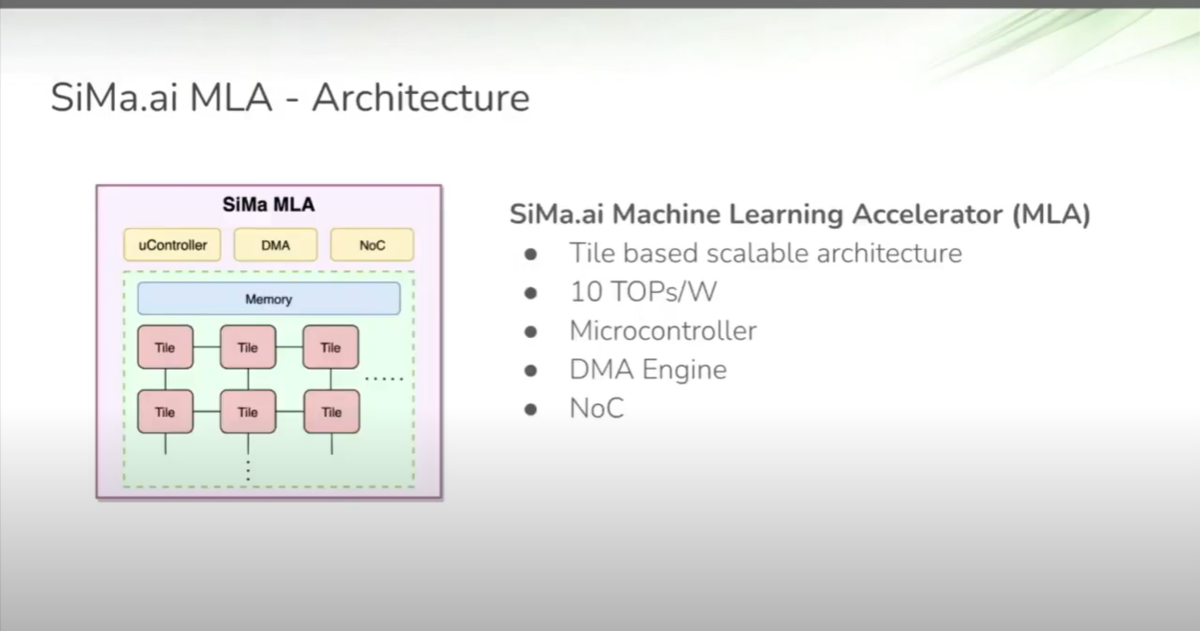

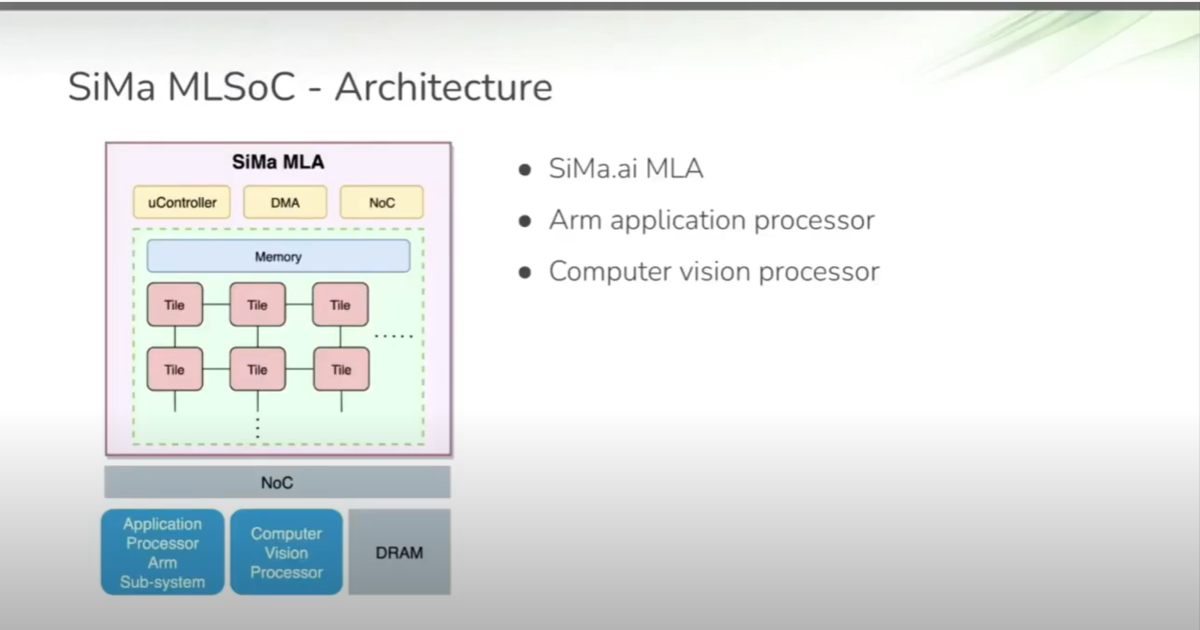

下図(0:35頃)では、初めて、MLA Architecture の概要ブロック図が公開されました。

Memory (ここには書いてありませんが、上記の講演のQ&Aで20MBということでした) + Tile ベースのコアが2次元に並んでいますね。NoCが付いているのは複数のMLAを接続したときのためのものでしょう。

「The Linley Spring Processor Conference 2020」の「SiMa.ai: High Performance, Green Machine Learning for Embedded Edge Systems」の時の MLAの説明では複数個のMLAの使い方が書いてありましたので、再度、見てみましょう。

AXI/INTERCONNECT とありますね。NoCはAXIで、この部分に、 Ariteris NoC を使っているんでしょうね。

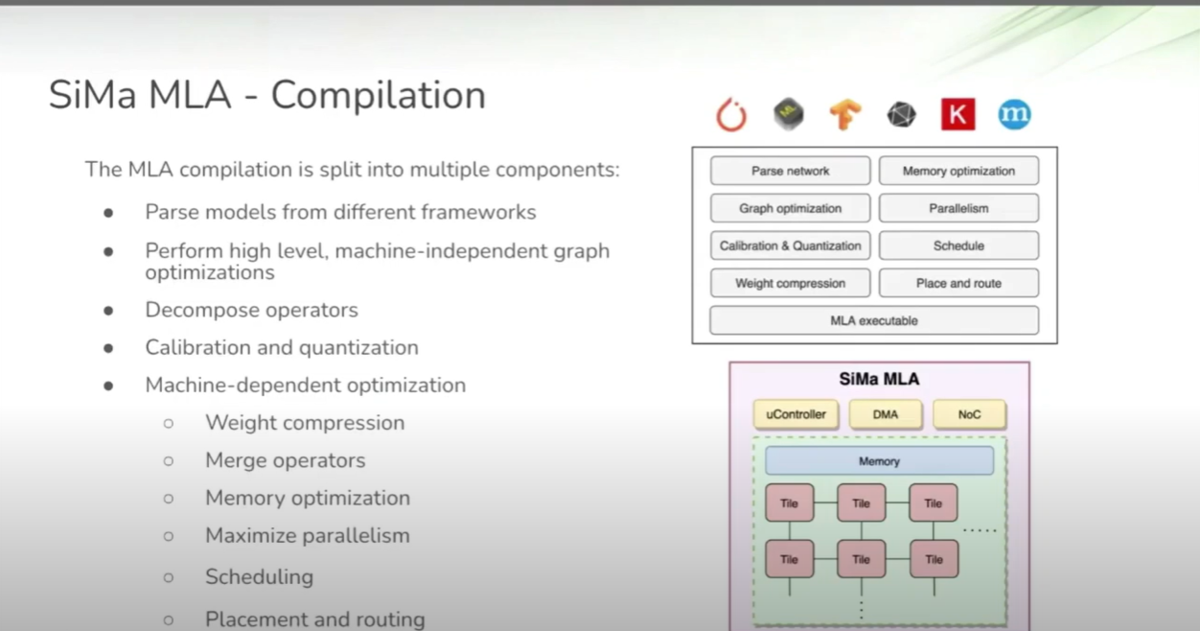

下図(0:52頃)では、SiMa MLA - Compilation の説明。MLA executable の下で SiMa MLA を使っている感じですね。

Machine-dependent optimization では、

- Weight compression

- Merge operators

- Memory optimization

- Maximize parallelism

- Scheduling

- Placement and routing

の処理をしているようです。

ポイントはやっぱり、Placement and routing ですよ。

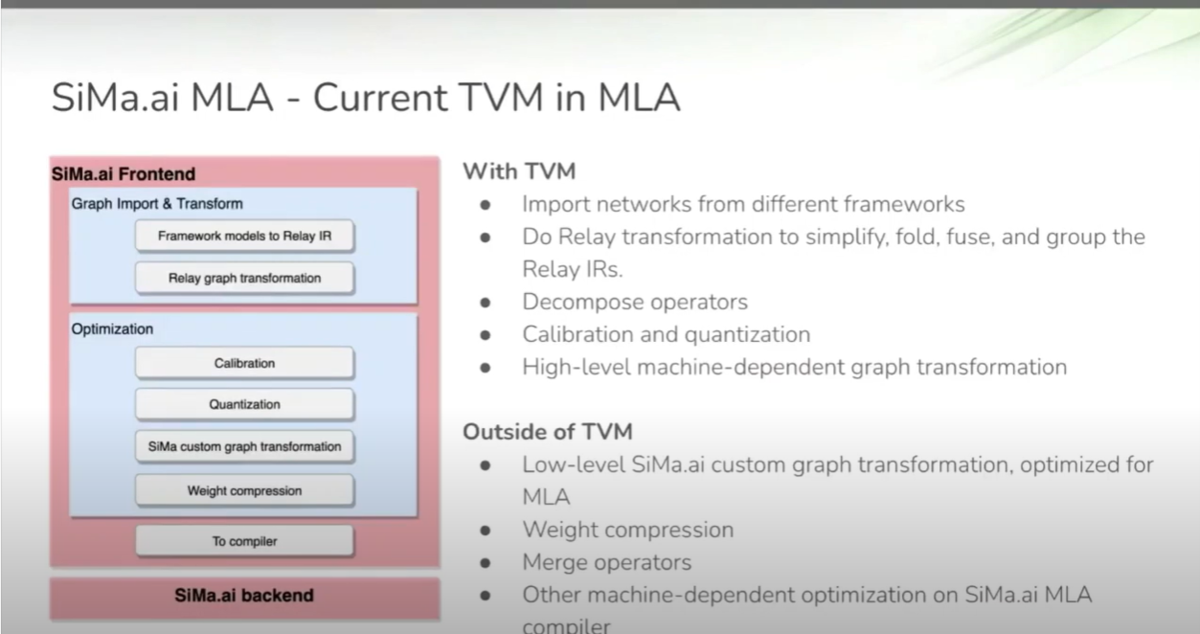

下図(1:38頃)では、SiMa.ai MLA の Current TVM in MLA にて、SiMa.ai Frontend では、TVMを使っているところと、TVMを使っていない(独自部分)の説明がありますね。

下図( 2:54頃)では、SiMa MLSoC - Architecture のブロック図です。SiMa.ai MLA, Arm appication processor, Computer vision processor の関係が分かります。

SiMa MLA内の NoC とは別の NoC で、Application Processor Arm Sub-system、Computer Vision Processor, DRAM と接続しているのが分かります。

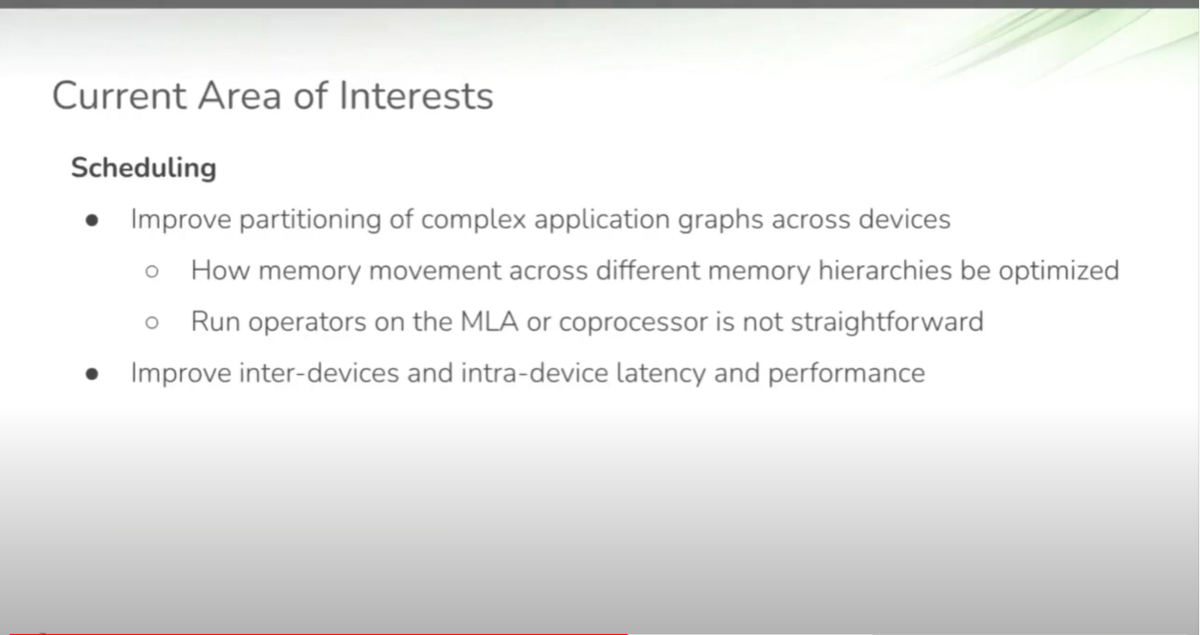

下図(3:14頃)では、MLSoC での TVM の Scheduling の説明です。グラフを各ユニットに分割して、メモリ階層の違いを意識してデータ移動する。ヘテロなハードウェアでのTVMの runtime 環境の実装例ですね。

下図は、TVM Conf - Day 1 - Keynote and Community Update の講演ビデオの51:37頃のOctoMLのスライドで、SiMa.ai のロゴが載っているので、OctoMLが協力しているということが分かりますね。

www.youtube.com

まとめ、

SiMa.ai の MLSoC は、カメラ(MIPI x4)から入力された動画を Camera ISP にて前処理した後に、CPU + MLA を TVMベースにてドライブするというものだということが分かりました。

なお、Computer Vision IP (Synopsys EV74はTVMで使っていないようです。

MLA は、AXI I/F のモジュールで、Tileベースのコアが2次元に並んでいて、内部に20MBのSRAMを搭載しています。外部DRAMのLPDDR4との内部SRAMとのデータ移動は専用のDMAにて行っています。

MLA 内の Tile ベースのコアの詳細は残念ながらまだわかっていませんんが、SoC全体の構成およびMLAの使い方については普通の使い方だと思いました。

参考:

TVM Conf 2020 - Day 1 - TVM at Synopsys and ITRI (Synopsys EV7x の TVM対応のビデオ)

www.youtube.com