はじめに

Cerebras SystemsがCS-3を発表

概略は、

- 発表日 : 2024.3

- 46,225 mm2 silicon

- 4 Trillion transistor

- AI optimizd cores 900,000

- 44 Gigabytes on-chip memory

- 21 Petabyte/s memory bandwidth

- 214 Petabit/s fabric bandbidth

- Process technology at TSMC 5nm

な感じ。

CS-1/CS-2/CS-3の比較

下図は、CS-1/CS-2/CS-3の比較です。

注目すべき点は、AI optimized cores が 850,000 => 900,000 と5%程度しか増えていないのに、トランジスタ数が大幅に増えていること (2.6 => 4)

この理由は、

Each CS-3 core has 8-wide FP16 SIMD units, a 2x increase over CS-2

ということのようです。各AI optimized core 内の計算機が倍強になったということ。

これにより、計算能力はざっくり2倍強。

しかしながら、下記の3つについては変わらず。

- Gigabytes on-chip memory

- Petabyte/s memory bandwidth

- Petabit/s fabric bandbidth

どこかにボトルネックがありそう。。

WSE内の各AI optimized core内の計算能力を2Xにしても内部の fbric bandwidthは変わらないということは各AI optimized coreへのデータ(パラメータ)の共有は間に合っている?

となると、WSEへのデータ供給が間に合っていない?

Ethernet?

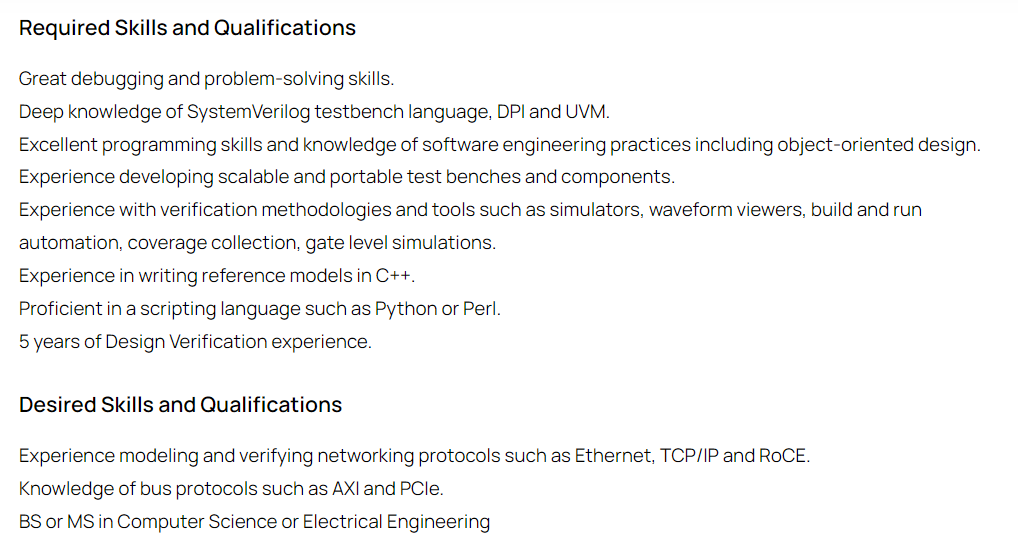

そのヒントは職にあった

Cerebras Systems のこの職。絶対になくなるので、スクリーンショット

WSE の両端にはASICではなく、FPGAが繋がっていると妄想しています。12本の100GbE が両端のFPGAに繋がっている(各FPGAに何本のFPGAが繋がっているかまでは不明)

この部分はCS-1から変わっていないと思うので、2019.8月より前にあったFPGAで実装。

その部分をASICにするので上記の職を募集しているのかな?と妄想

詳細は、かきのようになっている。

Desired Skills and Qualifications Experience modeling and verifying networking protocols such as Ethernet, TCP/IP and RoCE. Knowledge of bus protocols such as AXI and PCIe. BS or MS in Computer Science or Electrical Engineerins

PCIe & AIX & Ethenet & RoCE

これ、NVIDIA MellanoxのConnectX-? のようなASICを作ろうとしているのでは?

ただし、PCIeからデータが出入りするのではなく、WSEと。。

CS-1/CS-2では、100GbE x 12 だったのを、400GbE x n に変えたいのかな?と

おわりに

CS-1が 16nm、CS-2が 7nm だったので、CS-3は 3nm かな?と思っていましたが、5nm でとりあえず出してきましたね。。。次は Ethernet を強化した CS-3X なるものが出てきて、システム前端の性能アップを目指すのかな?と思っています。

当たるかな?

関連記事